Form 6-K ASML HOLDING NV For: Nov 24

�

�

SECURITIES AND EXCHANGE COMMISSION

Washington, D.C. 20549

�

�

FORM 6-K

�

�

REPORT OF A FOREIGN ISSUER

PURSUANT TO RULE 13A-16 OR 15D-16

OF THE SECURITIES EXCHANGE ACT OF 1934

For November�24, 2014

�

�

ASML Holding N.V.

�

�

De Run 6501

5504 DR Veldhoven

The Netherlands

(Address of principal executive offices)

�

�

Indicate by check mark whether the registrant files or will file annual reports under cover of Form 20-F or Form 40-F.

Form 20-F��x������������Form 40-F���

Indicate by check mark whether the registrant by furnishing the information contained in this Form is also thereby furnishing the information to the Commission pursuant to Rule 12g3-2(b) under the Securities Exchange Act of 1934.

Yes���������������No� �x

If �Yes� is marked, indicate below the file number assigned to the registrant in connection with Rule 12g3-2(b):������������

�

�

�

�

| Exhibits |

�� | � |

| 99.1 | �� | �ASML Outlines Long-Term Growth Opportunity at Investor Day; Receives First Order for EUV Production Systems�, press release date November 24, 2014 |

| 99.2 | �� | �Creating value for all stakeholders�, presentation dated November 24, 2014 |

| 99.3 | �� | �Many ways to shrink: The right moves to 10 nanometer and beyond�, presentation dated November�24, 2014 |

| 99.4 | �� | �DUV�, presentation dated November 24, 2014 |

| 99.5 | �� | �Holistic Lithography�, presentation dated November 24, 2014 |

| 99.6 | �� | �EUV�, presentation dated November 24, 2014 |

| 99.7 | �� | �Market Update�, presentation dated November 24, 2014 |

| 99.8 | �� | �Financial Model�, presentation dated November 24, 2014 |

| 99.9 | �� | �Closing Remarks�, presentation dated November 24, 2014 |

SIGNATURES

Pursuant to the requirements of the Securities Exchange Act of 1934, the registrant has duly caused this report to be signed on its behalf by the undersigned, thereunto duly authorized.

�

| � | � | ASML HOLDING N.V. (Registrant) | ||||

| Date: November�24, 2014 | � | � | By: | � | /s/ Peter T.F.M. Wennink | |

| � | � | � | Peter T.F.M. Wennink | |||

| � | � | � | Chief Executive Officer | |||

Exhibit 99.1

�

�

ASML Outlines Long-Term Growth Opportunity at Investor Day; Receives First Order for EUV Production Systems

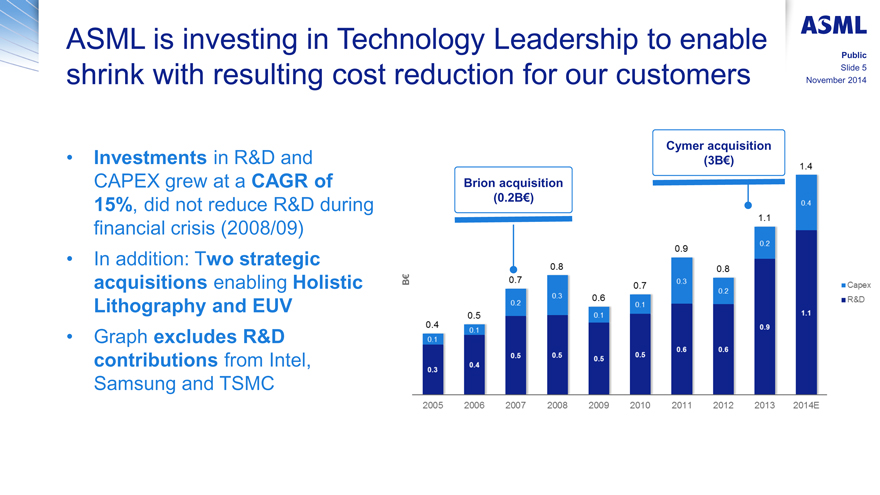

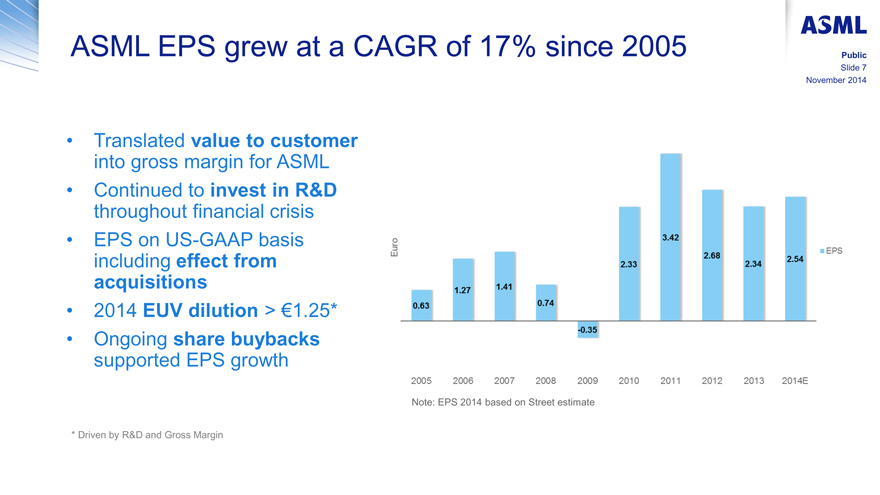

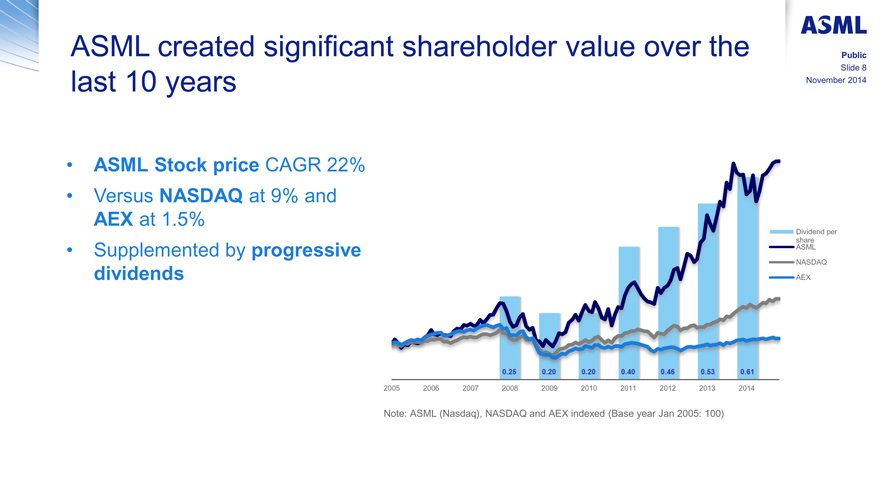

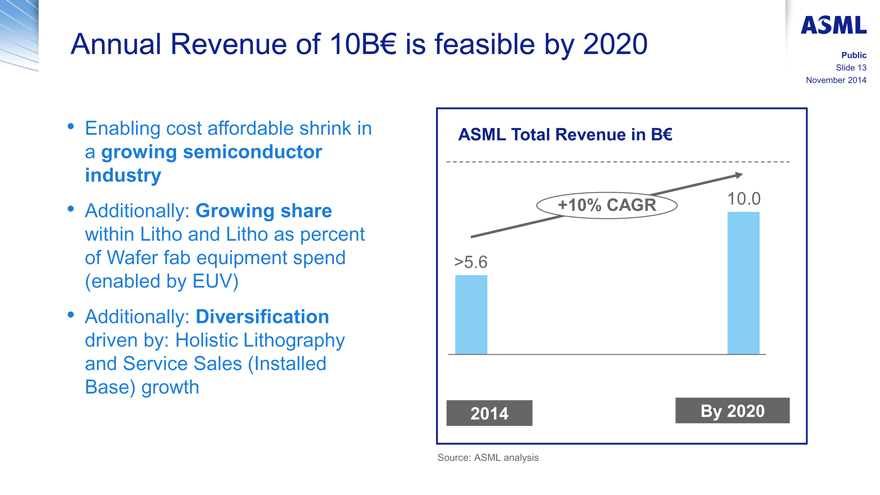

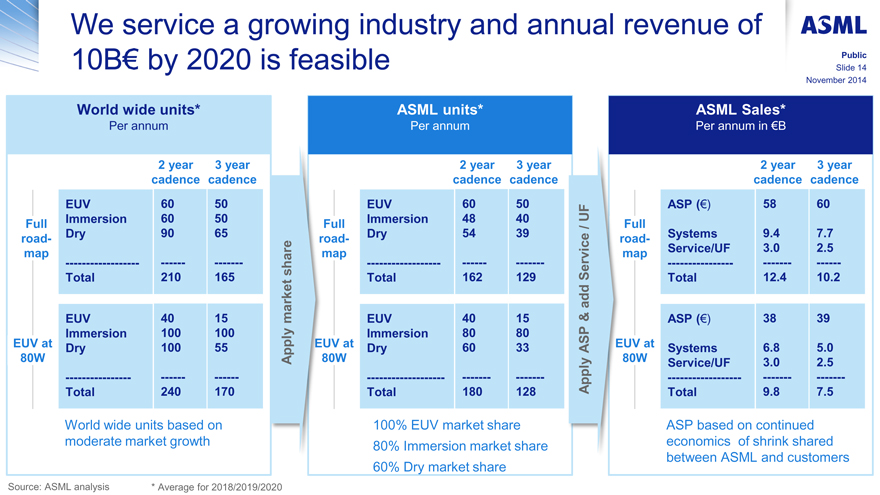

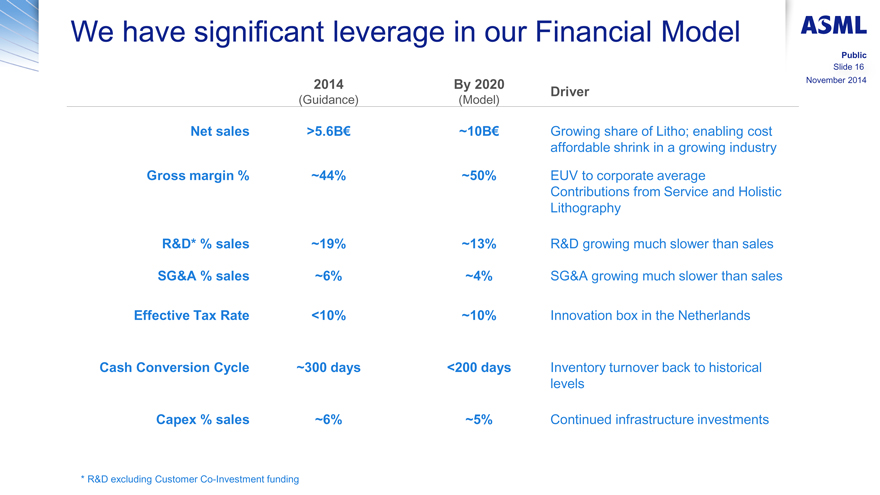

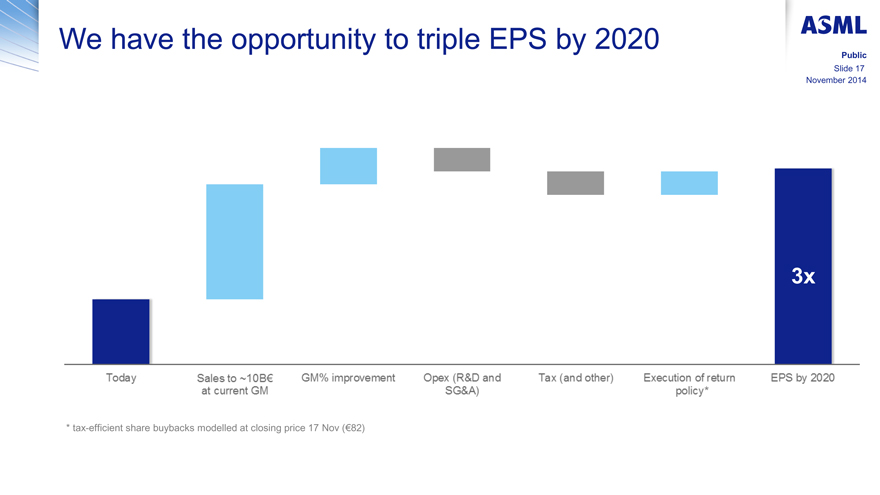

LONDON, 24�November 2014 - At its Investor Day, ASML Holding N.V. (ASML) will today outline its expected opportunity to grow net sales to about EUR 10 billion and to triple earnings per share by 2020.

ASML also announces that Taiwan Semiconductor Manufacturing Company Ltd. (TSMC) has ordered two NXE:3350B EUV systems for delivery in 2015 with the intention to use those systems in production. In addition, two NXE:3300B systems already delivered to TSMC will be upgraded to NXE:3350B performance.

ASML�s executive management will present the 2020 ambition in more detail from 13:00 GMT (14:00 CET) at the Investor Day in London. The presentations will also be webcast live at www.asml.com.

Underpinning ASML�s 2020 ambition is the semiconductor industry�s continued aggressive pursuit of transistor scaling to deliver improvements in performance, size and power consumption, which in turn makes possible new applications and more attractive consumer devices and services, fuelling overall industry growth. In short, ASML expects Moore�s Law to continue to drive the industry in the coming ten years, with lithography as the key enabler.

Regarding our main technologies, we expect

Deep-UV immersion systems to be used for patterning of multiple layers in all advanced processes for the forseeable future;

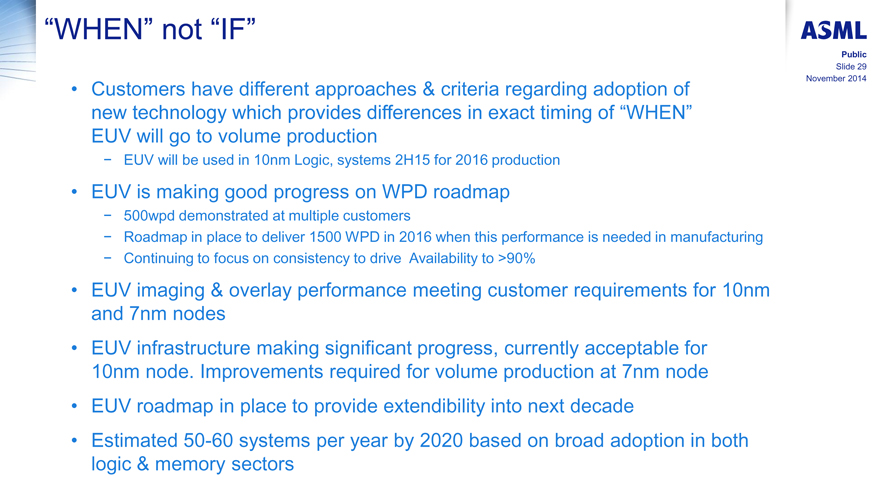

EUV to enable cost effective manufacturing of logic, DRAM and NAND chips from 2016/2017 allowing feature size shrink and simplification of manufacturing processes;

Holistic Lithography products to deliver advanced correction capability supporting the tightening of litho related manufacturing tolerances, resulting in lower rework and higher yields.

About ASML ASML makes possible affordable microelectronics that improve the quality of life. ASML invents and develops complex technology for high-tech lithography machines for the semiconductor industry. ASML�s guiding principle is continuing Moore�s Law towards ever smaller, cheaper, more powerful and energy-efficient semiconductors. Our success is based on three pillars: technology leadership combined with customer and supplier intimacy, highly efficient processes and entrepreneurial people. We are a multinational company with over 70 locations in 16 countries, headquartered in Veldhoven, the Netherlands. We employ more than 13,800 people on payroll and flexible contracts (expressed in full time equivalents). Our company is an inspiring place where employees work, meet, learn and share. ASML is traded on Euronext Amsterdam and NASDAQ under the symbol ASML. More information about ASML, our products and technology, and career opportunities is available on: www.asml.com

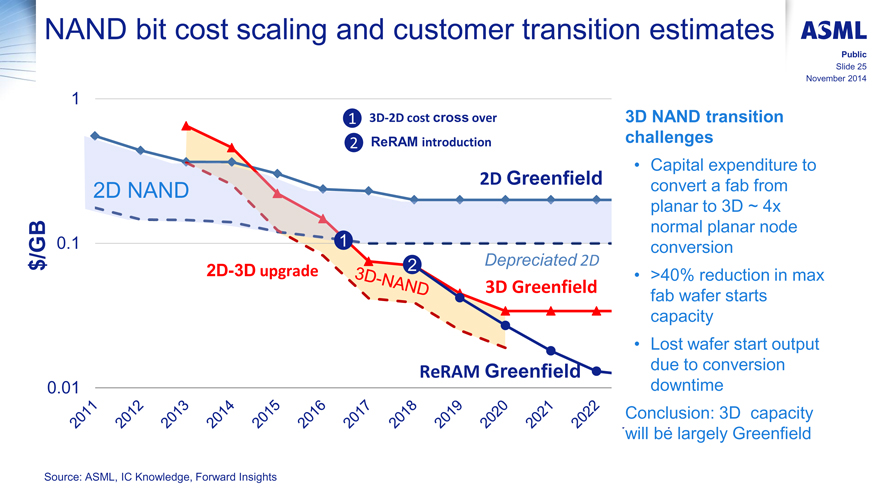

Forward Looking Statements This document contains statements relating to certain projections and business trends that are forward-looking, including statements with respect to our outlook, expected customer demand in specified market segments, expected sales levels and trends, our market share, customer orders and systems backlog, IC unit demand, expected or indicative financial results or targets, including revenue, gross margin, expenses, gross margin percentage, opex percentage of sales, tax percentage, cash conversion cycle, capex percentage of sales, credit rating and earnings per share, expected shipments of tools and the timing thereof, including expected shipments of EUV and DUV tools, productivity of our tools and systems performance, including EUV system performance (such as endurance tests), the development of EUV technology and timing of shipments, development in IC technology, including shrink scenarios, NAND technology development and cost estimates, expectations on development of the shrink roadmap across all of our systems, upgradeability of

ASML

Page 1 of 3

�

our tools, system and upgrade orders, customer transition estimates, expected transition scaling, forecasted industry developments, including expected smartphone, tablet and server use in future years, and expectations relating to new applications including wearable devices and connected devices, expected investment pay-back time for foundries, expected construction of additional holistic lithography infrastructure, the continuation of Moore�s Law, and our dividend policy and intention to repurchase shares. You can generally identify these statements by the use of words like �may�, �will�, �could�, �should�, �project�, �believe�, �anticipate�, �expect�, �plan�, �estimate�, �forecast�, �potential�, �intend�, �continue� and variations of these words or comparable words. These statements are not historical facts, but rather are based on current expectations, estimates, assumptions and projections about the business and our future financial results and readers should not place undue reliance on them.

Forward-looking statements do not guarantee future performance and involve risks and uncertainties. These risks and uncertainties include, without limitation, economic conditions, product demand and semiconductor equipment industry capacity, worldwide demand and manufacturing capacity utilization for semiconductors (the principal product of our customer base), the impact of general economic conditions on consumer confidence and demand for our customers� products, competitive products and pricing, affordability of shrink, the continuation of Moore�s Law, the impact of manufacturing efficiencies and capacity constraints, performance of our systems, the continuing success of technology advances and the related pace of new product development and customer acceptance of new products and customers meeting their own development roadmaps, market demand for our existing products and for new products and our ability to maintain or increase or market share, the development of and customer demand for multi-patterning technology and our ability to meet overlay and patterning requirements, the number and timing of EUV systems expected to be shipped, our ability to enforce patents and protect intellectual property rights, the risk of intellectual property litigation, EUV system performance and customer acceptance, availability of raw materials and critical manufacturing equipment, trade environment, our ability to reduce costs, changes in exchange rates and tax rates, available cash, distributable reserves for dividend payments and share repurchases, changes in our treasury policy, including our dividend and repurchase policy, failure to complete orders, including due to failure to meet purchase order performance conditions (for new systems and upgrades), the risk that key assumptions underlying financial targets prove inaccurate, including assumptions relating to market share, lithography market growth and our customers� ability to reduce productions costs, risks associated with Cymer, which we acquired in 2013, and other risks indicated in the risk factors included in ASML�s Annual Report on Form 20-F and other filings with the US Securities and Exchange Commission. These forward-looking statements are made only as of the date of this document. We do not undertake to update or revise the forward-looking statements, whether as a result of new information, future events or otherwise.

Lucas van Grinsven

Communication Worldwide | Corporate

+316 101 99 532

Niclas Mika

Corporate Communications

+31 6 201 528 63

Craig DeYoung

VP Investor Relations Worldwide

+1.480.696.2762

Page 2 of 3

ASML

�

Marcel Kemp

Director Investor Relations - Europe

+31.40.268.6494

Copyright 2012 (ASML) All rights reserved

ASML.com > Press > Press Releases > ASML Outlines Long-Term Growth...

ASML

Page 3 of 3

Exhibit 99.2

�

�

ASML

Creating value for all stakeholders

Peter Wennink

President & Chief Executive Officer

24 November 2014

INVESTOR DAY

ASMLSMALLTALK2014

LONDON

�

Forward looking statements

ASML

Public

Slide 2

November 2014

This document contains statements relating to certain projections and business trends that are forward-looking, including statements with respect to our outlook, expected customer demand in specified market segments, expected sales levels and trends, our market share, customer orders and systems backlog, IC unit demand, expected or indicative financial results or targets, including revenue, gross margin, expenses, gross margin percentage, opex percentage of sales, tax percentage, cash conversion cycle, capex percentage of sales, credit rating and earnings per share, expected shipments of tools and the timing thereof, including expected shipments of EUV and DUV tools, productivity of our tools and systems performance, including EUV system performance (such as endurance tests), the development of EUV technology and timing of shipments, development in IC technology, including shrink scenarios, NAND technology development and cost estimates, expectations on development of the shrink roadmap across all of our systems, upgradeability of our tools, system orders, customer transition estimates, expected transition scaling, forecasted industry developments, including expected smartphone, tablet and server use in future years, and expectations relating to new applications including wearable devices and connected devices, expected investment pay-back time for foundries, expected construction of additional holistic lithography infrastructure, the continuation of Moore�s Law, and our dividend policy and intention to repurchase shares. You can generally identify these statements by the use of words like �may�, �will�, �could�, �should�, �project�, �believe�, �anticipate�, �expect�, �plan�, �estimate�, �forecast�, �potential�, �intend�, �continue� and variations of these words or comparable words. These statements are not historical facts, but rather are based on current expectations, estimates, assumptions and projections about the business and our future financial results and readers should not place undue reliance on them.

Forward-looking statements do not guarantee future performance and involve risks and uncertainties. These risks and uncertainties include, without limitation, economic conditions, product demand and semiconductor equipment industry capacity, worldwide demand and manufacturing capacity utilization for semiconductors (the principal product of our customer base), the impact of general economic conditions on consumer confidence and demand for our customers� products, competitive products and pricing, affordability of shrink, the continuation of Moore�s Law, the impact of manufacturing efficiencies and capacity constraints, performance of our systems, the continuing success of technology advances and the related pace of new product development and customer acceptance of new products and customers meeting their own development roadmaps, market demand for our existing products and for new products and our ability to maintain or increase or market share, the development of and customer demand for multi-patterning technology and our ability to meet overlay and patterning requirements, the number and timing of EUV systems expected to be shipped, our ability to enforce patents and protect intellectual property rights, the risk of intellectual property litigation, EUV system performance and customer acceptance, availability of raw materials and critical manufacturing equipment, trade environment, our ability to reduce costs, changes in exchange rates and tax rates, available cash, distributable reserves for dividend payments and share repurchases, changes in our treasury policy, including our dividend and repurchase policy, completion of sales orders, the risk that key assumptions underlying financial targets prove inaccurate, including assumptions relating to market share, lithography market growth and our customers� ability to reduce productions costs, risks associated with Cymer, which we acquired in 2013, and other risks indicated in the risk factors included in ASML�s Annual Report on Form 20-F and other filings with the US Securities and Exchange Commission. These forward-looking statements are made only as of the date of this document. We do not undertake to update or revise the forward-looking statements, whether as a result of new information, future events or otherwise.

�

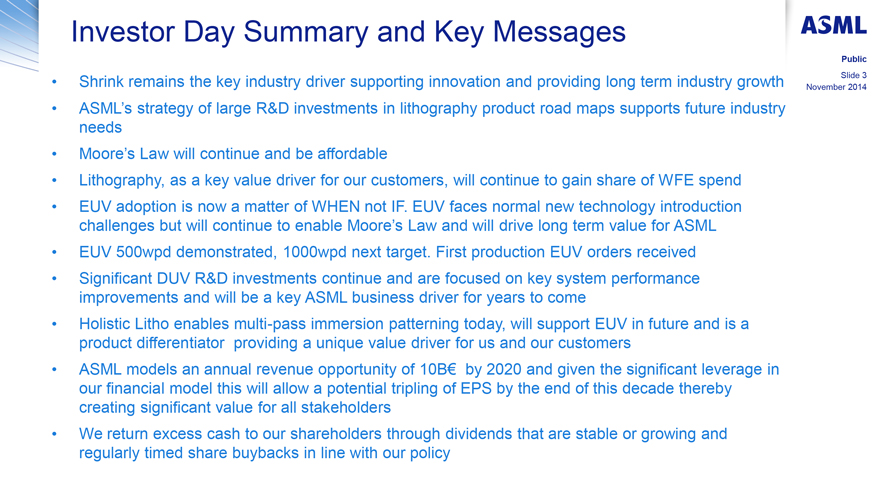

Summary: ASML�s positioning, opportunities and threats

ASML

Public

Slide 3

November 2014

ASML�s prime responsibility is to provide value for our customers, shareholders, employees, and supply chain partners

Our success is based on delivering Litho products with superior performance at lowest cost of ownership and on our flexible operating model required for an inherently volatile market

ASML models an annual total revenue opportunity of 10B€ by 2020 and subsequent growth beyond

We have reviewed our most impactful threats and feel confident about our approach to mitigate these

�

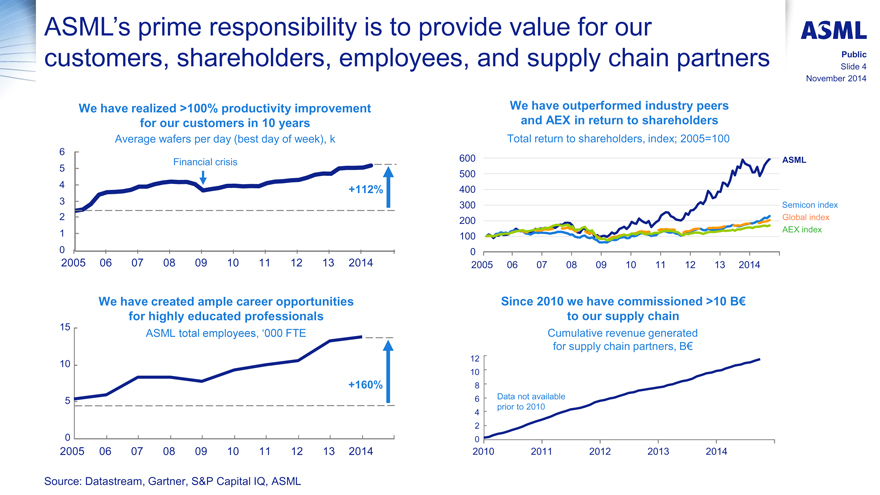

ASML�s prime responsibility is to provide value for our customers, shareholders, employees, and supply chain partners

ASML

Public

Slide 4

November 2014

We have realized >100% productivity improvement

for our customers in 10 years

Average wafers per day (best day of week), k

6

5

4

3

2

1

0

2005 06

Financial crisis

07

08

09

10

11

12

+112%

13 2014

600

500

400

300

200

100

0

2005

We have outperformed industry peers

and AEX in return to shareholders

Total return to shareholders, index; 2005=100

06

07

08

09

10

11

12

13

2014

ASML

Semicon index

Global index

AEX index

15

10

5

0

2005

We have created ample career opportunities

for highly educated professionals

ASML total employees, �000 FTE

06

07

08

09

10

11

12

+160%

13 2014

12

10

8

6

4

2

0

2010

Since 2010 we have commissioned >10 B€

to our supply chain

Cumulative revenue generated

for supply chain partners, B€

Data not available

prior to 2010

2011

2012

2013

2014

Source: Datastream, Gartner, S&P Capital IQ, ASML

�

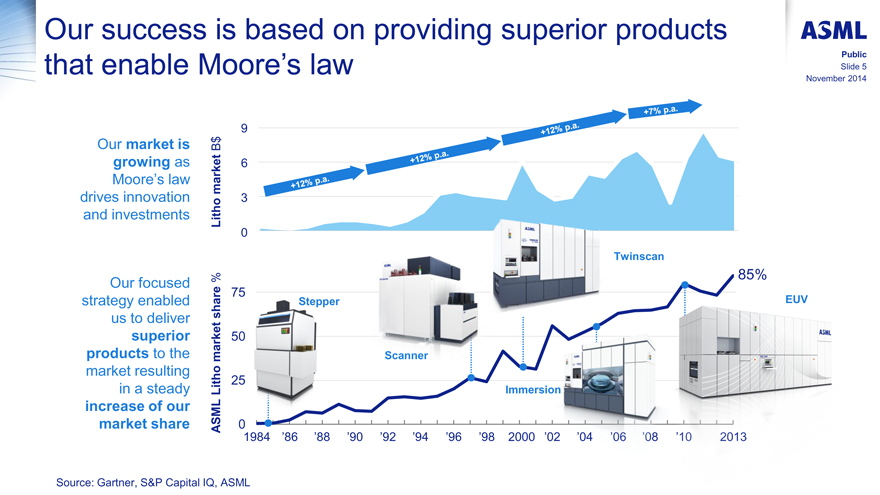

Our success is based on providing superior products that enable Moore�s law

ASML

Public

Slide 5

November 2014

Our market is growing as Moore�s law drives innovation and investments

Litho market B$

9

6

3

+12% p.a.

+12% p.a.

+12% p.a.

+7% p.a.

0

Our focused strategy enabled us to deliver superior products to the market resulting in a steady increase of our market share

ASML Litho market share %

75

Stepper

Scanner

Immersion

Twinscan

EUV

85%

50

25

0

1984

�86

�88

�90

�92

�94

�96

�98

�2000

�02

�04

�06

�08

�10

2013

Source: Gartner, S&P Capital IQ, ASML

�

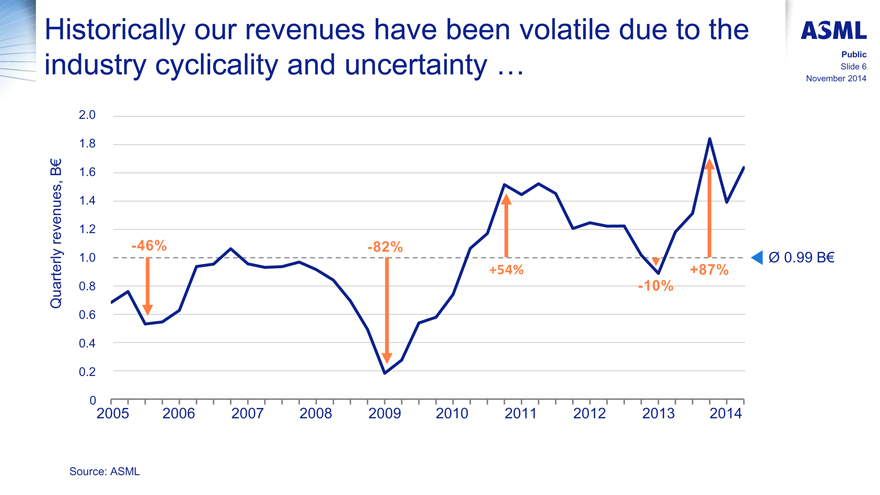

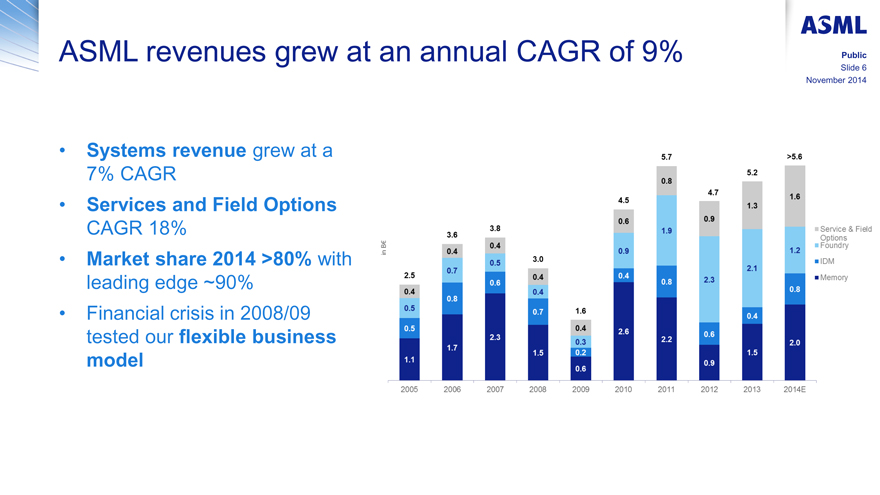

Historically our revenues have been volatile due to the industry cyclicality and uncertainty...

ASML

Public

Slide 6

November 2014

Quarterly revenues, B€

2.0

1.8

1.6

1.4

1.2

-46%

-82%

1.0

�0.99 B€

+54%

+87%

0.8

-10%

0.6

0.4

0.2

0

2005

2006

2007

2008

2009

2010

2011

2012

2013

2014

Source: ASML

�

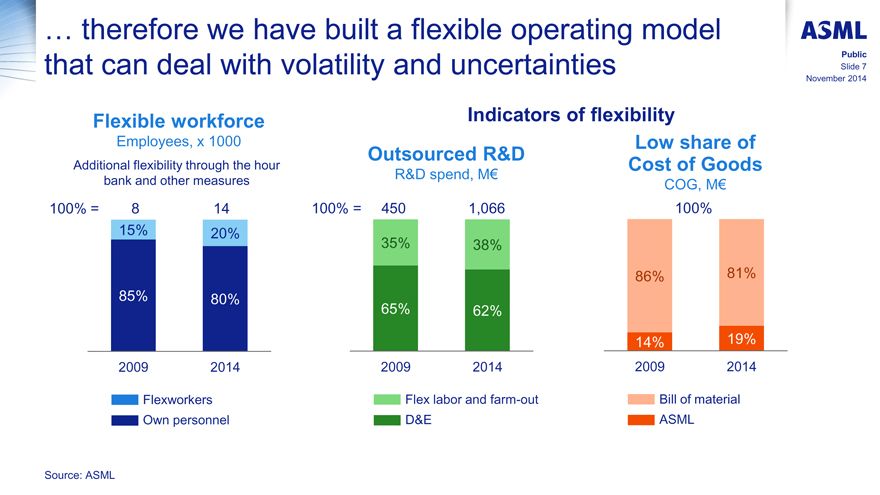

... therefore we have built a flexible operating model that can deal with volatility and uncertainties

ASML

Public

Slide 7

November 2014

Flexible workforce

Indicators of flexibility

Employees, x 1000

Low share of

Additional flexibility through the hour bank and other measures

Outsourced R&D

Cost of Goods

R&D spend, M€

COG, M€

100% =8

14

100% =

450

1,066

100%

15%

20%

86%

81%

35%

38%

85%

80%

65%

62%

14%

19%

2009

2014

2009

2014

2009

2014

Flexworkers

Flex labor and farm-out

Bill of material

Own personnel

D&E

ASML

Source: ASML

�

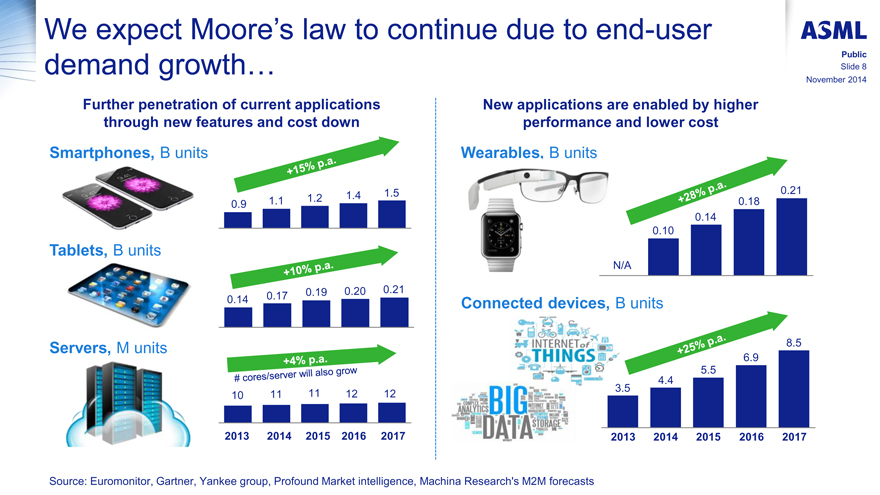

We expect Moore�s law to continue due to end-user demand growth...

ASML

Public

Slide 8

November 2014

Further penetration of current applications

New applications are enabled by higher

through new features and cost down

performance and lower cost

Smartphones, B units

Wearables, B units

+28% p.a.

+15% p.a.

0.21

0.9

1.1

1.2

1.4

1. 5

0.18

0.14

0.10

Tablets, B units

N/A

+10% p.a.

0.14

0.17

0.19

0.20

0.21

Connected devices, B units

Servers, M units

Internet of things

+25% p.a.

8.5

+4% p.a.

Big Data

6.9

# cores /server will also grow

5.5

4.4

10

11

11

12

12

3.5

2013

2014

2015

2016

2017

2013

2014

2015

2016

2017

Source: Euromonitor, Gartner, Yankee group, Profound Market intelligence, Machina Research�s M2M forecasts

�

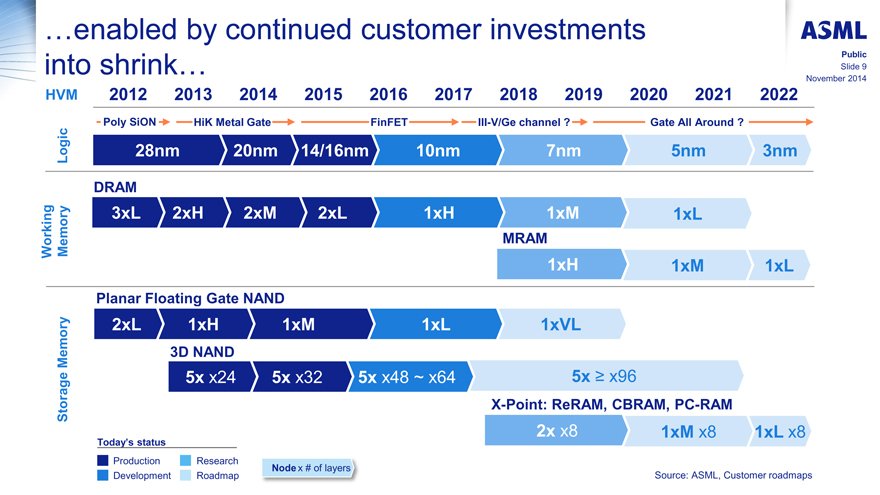

�enabled by continued customer investments into shrink

ASML Public Slide 9 November 2014

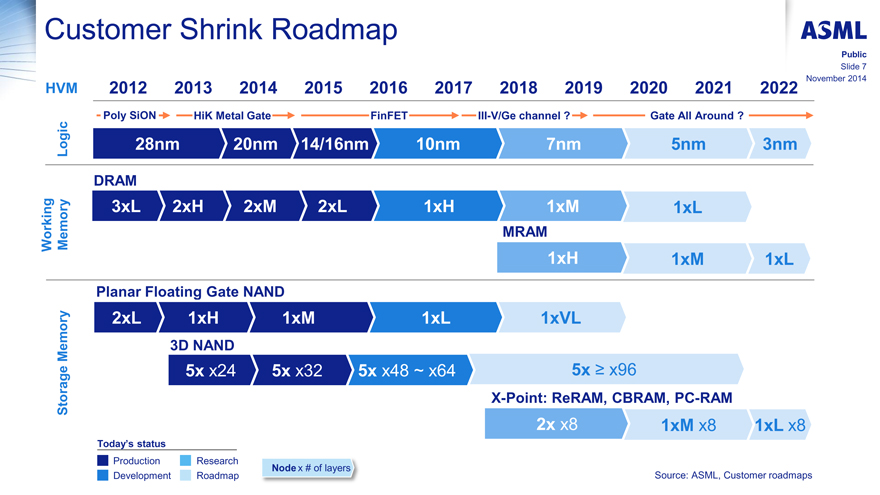

HVM 2012 2013 2014 2015 2016 2017 2018 2019 2020 2021 2022

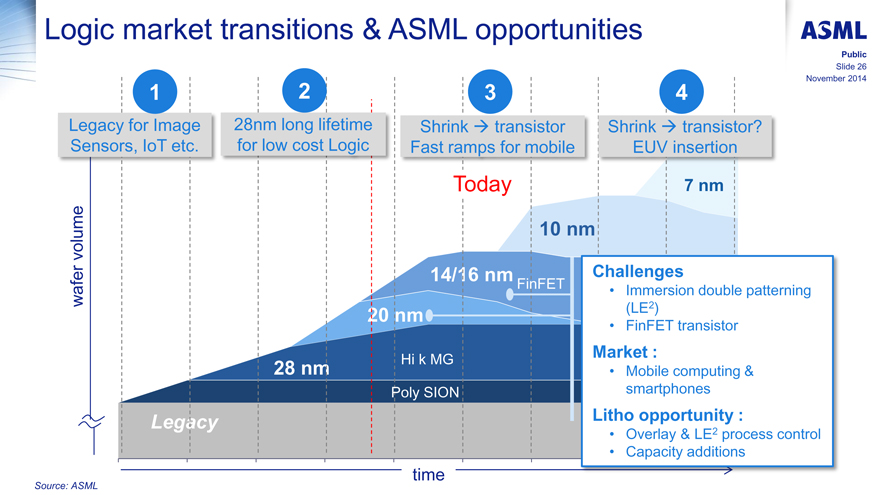

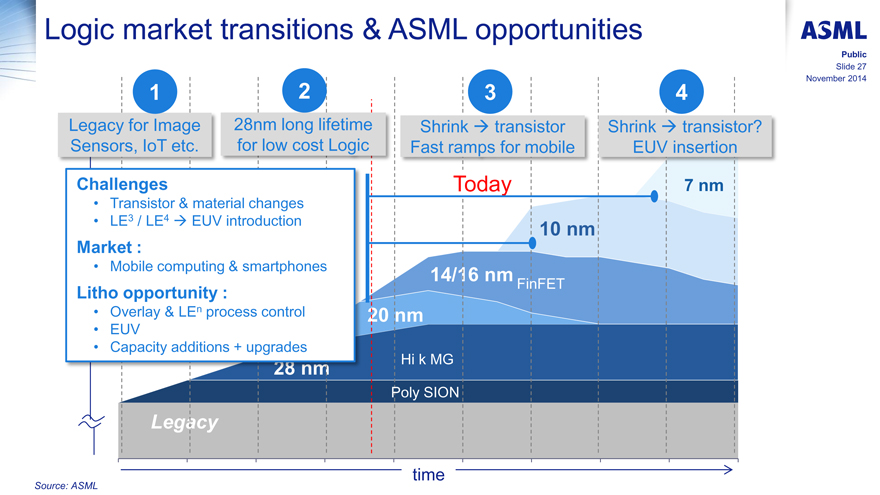

Logic Poly SiON HiK Metal Gate FinFET III-V/Ge channel ? Gate All Around ?

28nm 20nm 14/16nm 10nm 7nm 5nm 3nm

DRAM Working Memory 3xL 2xH 2xM 2xL 1xH 1xM 1xL

MRAM 1xH 1xM 1xL

Planar Floating Gate NAND Storage Memory 2xL 1xH 1xM 1xL 1xVL

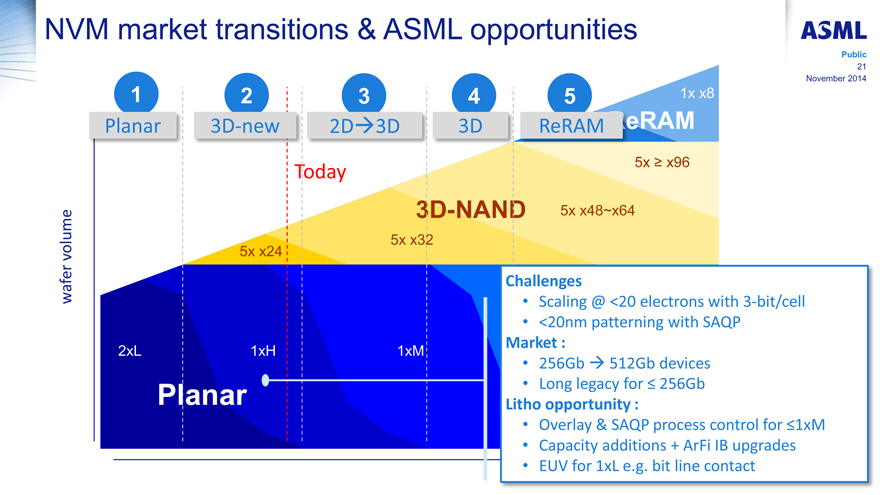

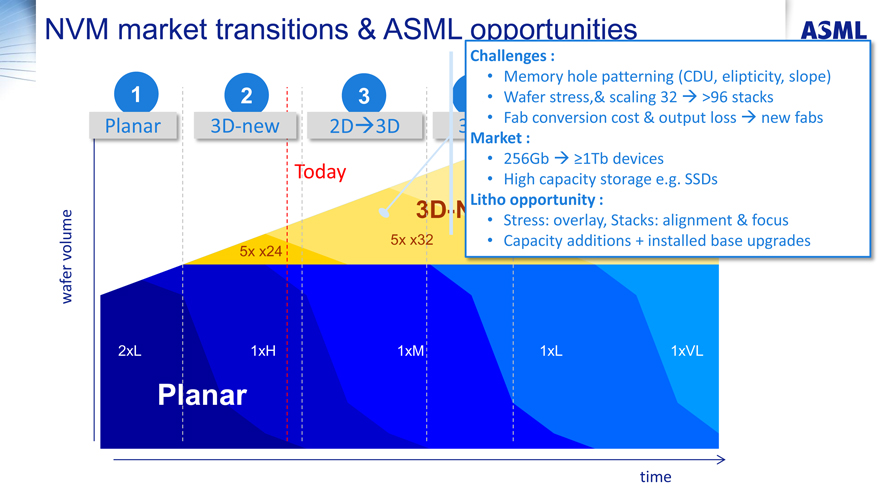

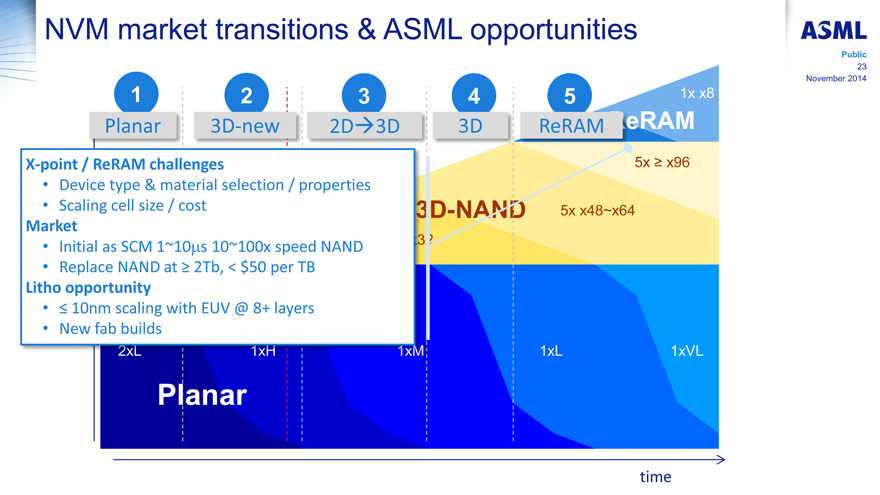

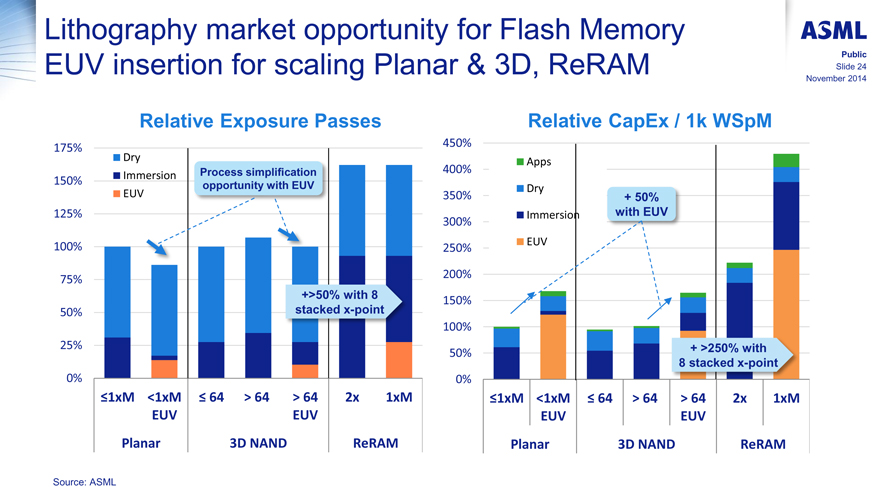

3D NAND 5x x24 5x x32 5x x48 ~ x64 5x � x96

X-Point: ReRAM, CBRAM, PC-RAM 2x x8 1xM x8 1xL x8

Today�s status

Production Development

Research Roadmap

Node x # of layers

Source: ASML, Customer roadmaps

�

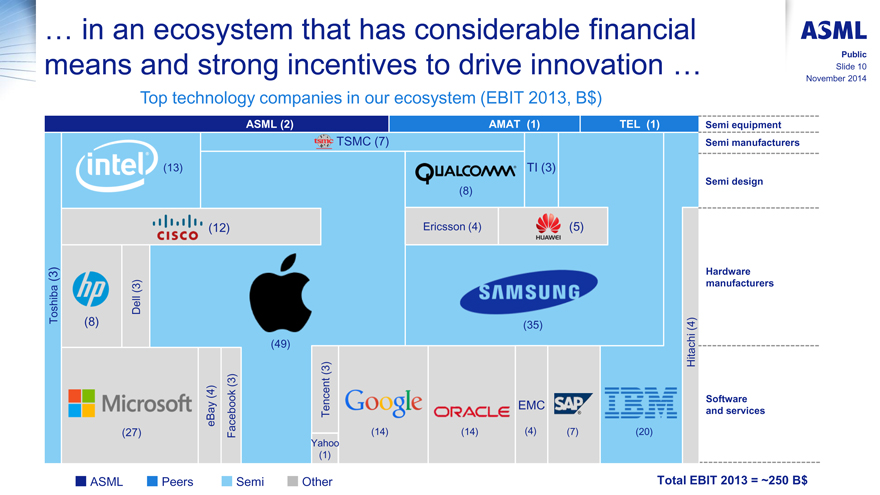

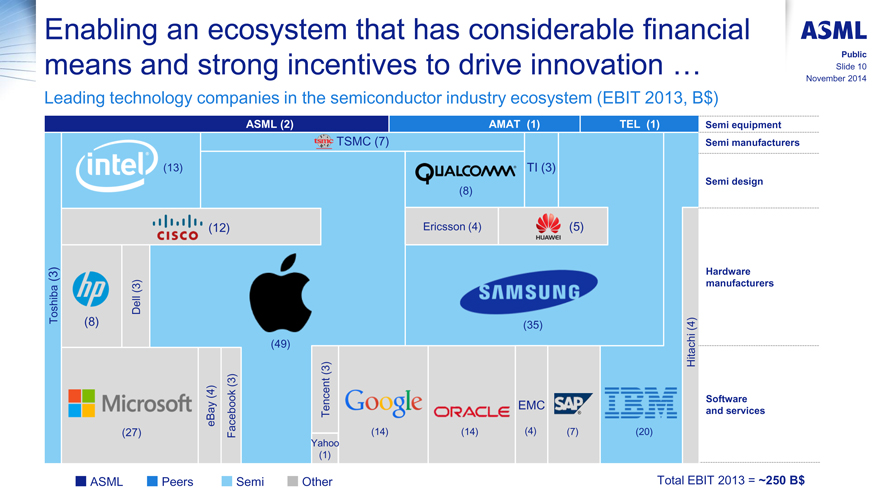

� in an ecosystem that has considerable financial means and strong incentives to drive innovation �

ASML Public Slide 10 November 2014

Top technology companies in our ecosystem (EBIT 2013, B$)

ASML (2) AMAT (1) TEL (1)

intel (13) TSMC (7)

Toshiba (3)

QUALCOMM� (8) TI (3) CISCO (12) Ericsson (4) HUAWEI (5) hp (8) Dell (3)

(49) SAMSUNG (35) Hitachi (4) Microsoft (27) eBay (4) Facebook (3) Tencent (3) Yahoo (1) Google (14) ORACLE (14)

EMC (4) SAP� (7) IBM (20)

Semi equipment

Semi manufacturers Semi design

Hardware manufacturers

Software and services

ASML Peers Semi Other

Total EBIT 2013 = ~250 B$

�

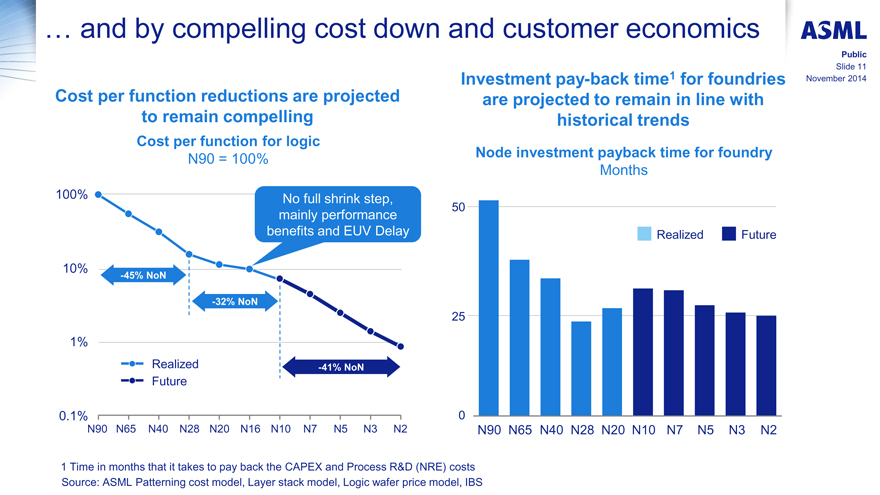

� and by compelling cost down and customer economics ASML Public Slide 11 November 2014

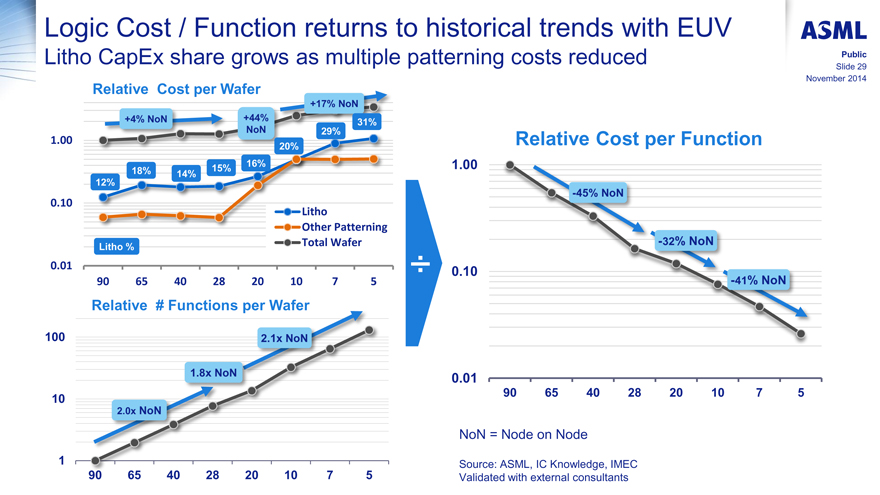

Cost per function reductions are projected to remain compelling

Cost per function for logic N90 = 100%

100% 10% 1% 0.1%

No full shrink step, mainly performance benefits and EUV Delay

-45% NoN -32% NoN -41% NoN

Realized

Future

N90 N65 N40 N28 N20 N16 N10 N7 N5 N3 N2

Investment pay-back time1 for foundries are projected to remain in line with historical trends

Node investment payback time for foundry

Months

50 25 0

Realized

Future

N90 N65 N40 N28 N20 N10 N7 N5 N3 N2

1 Time in months that it takes to pay back the CAPEX and Process R&D (NRE) costs

Source: ASML Patterning cost model, Layer stack model, Logic wafer price model, IBS

�

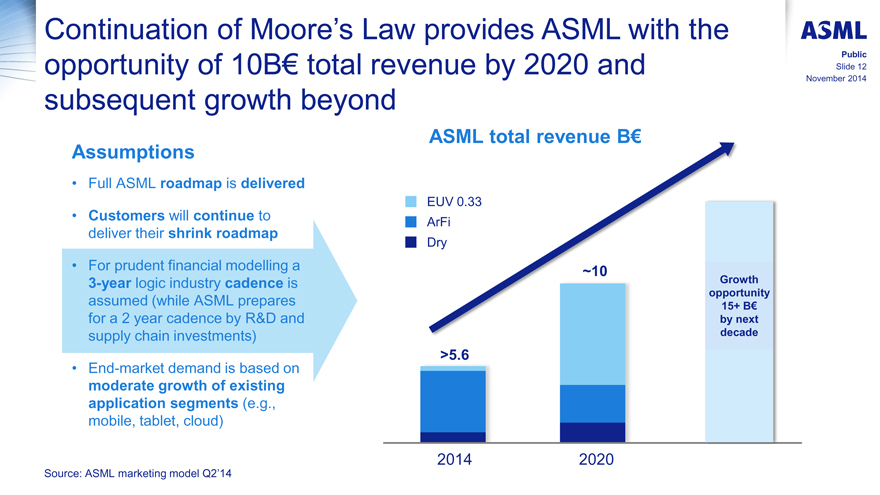

Continuation of Moore�s Law provides ASML with the opportunity of 10B€ total revenue by 2020 and subsequent growth beyond

ASML Public Slide 12 November 2014

Assumptions

Full ASML roadmap is delivered

Customers will continue to deliver their shrink roadmap

For prudent financial modelling a 3-year logic industry cadence is assumed (while ASML prepares for a 2 year cadence by R&D and supply chain investments)

End-market demand is based on moderate growth of existing application segments (e.g., mobile, tablet, cloud)

ASML total revenue B€

EUV 0.33

ArFi

Dry

>5.6

~10

Growth opportunity 15+ B€ by next decade

2014 2020

Source: ASML marketing model Q2�14

�

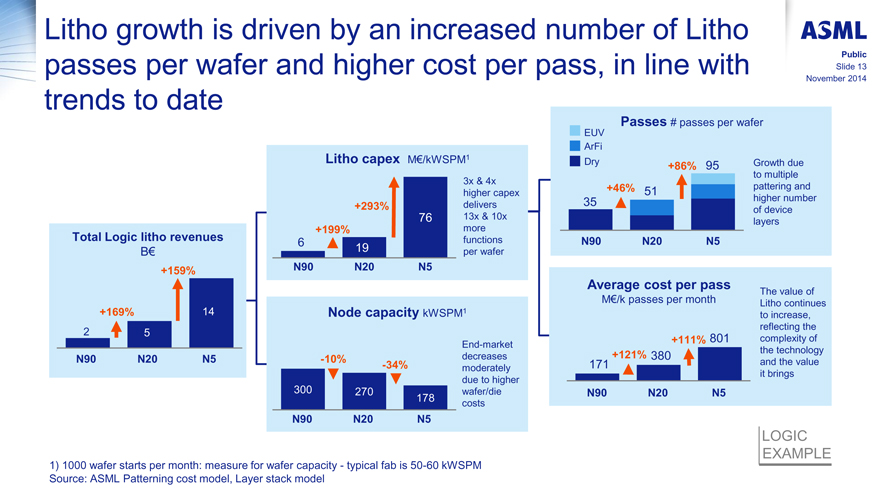

Litho growth is driven by an increased number of Litho passes per wafer and higher cost per pass, in line with trends to date

ASML Public Slide 13 November 2014

Total Logic litho revenues

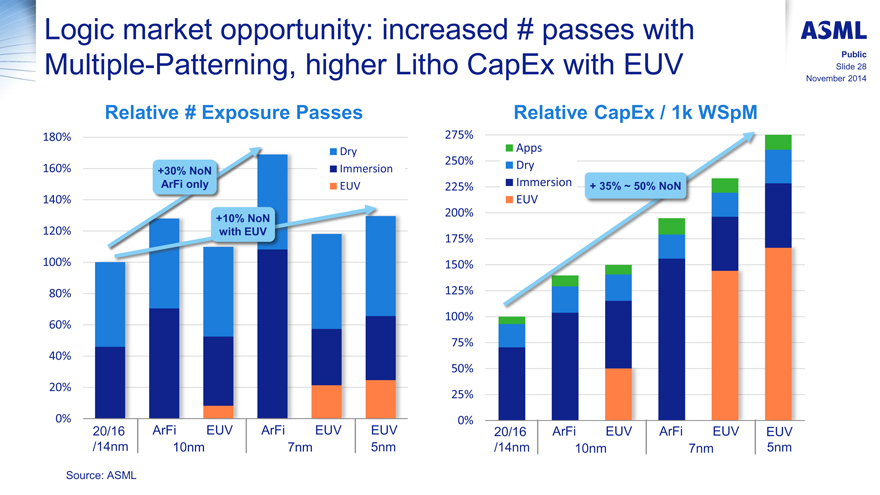

B€ +159% +169% 2 5 14

N90 N20 N5

Litho capex M€/kWSPM1

6 +199% +293% 19 76

3x & 4x higher capex delivers 13x & 10x more functions per wafer

N90 N20 N5

Node capacity kWSPM1

-10% 300 270 -34%

178

End-market decreases moderately due to higher wafer/die costs

N90 N20 N5

Passes # passes per wafer

EUV ArFi Dry

35 +46% 51 +86% 95

Growth due to multiple pattering and higher number of device layers

N90 N20 N5

Average cost per pass

M€/k passes per month

171 +121% 380 +111% 801

The value of Litho continues to increase, reflecting the complexity of the technology and the value it brings

N90 N20 N5

LOGIC EXAMPLE

1) 1000 wafer starts per month: measure for wafer capacity - typical fab is 50-60 kWSPM

Source: ASML Patterning cost model, Layer stack model

�

We have reviewed our most impactful threats

ASML Public Slide 14 November 2014

ASML

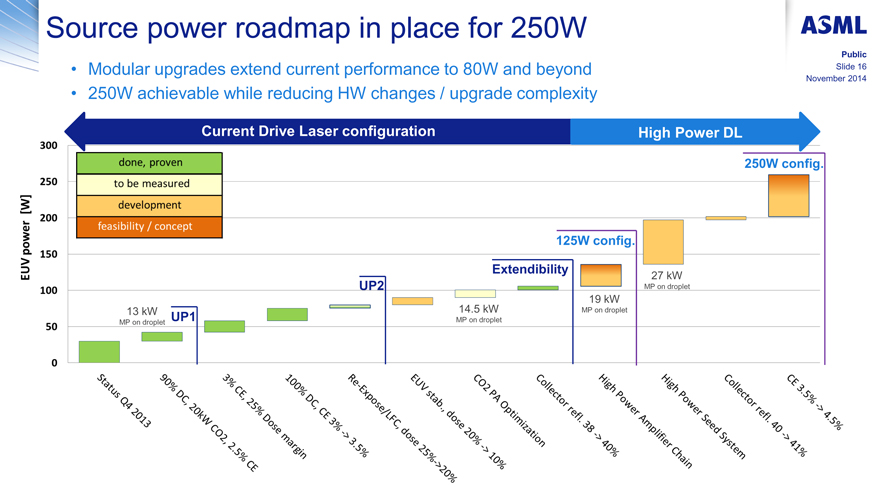

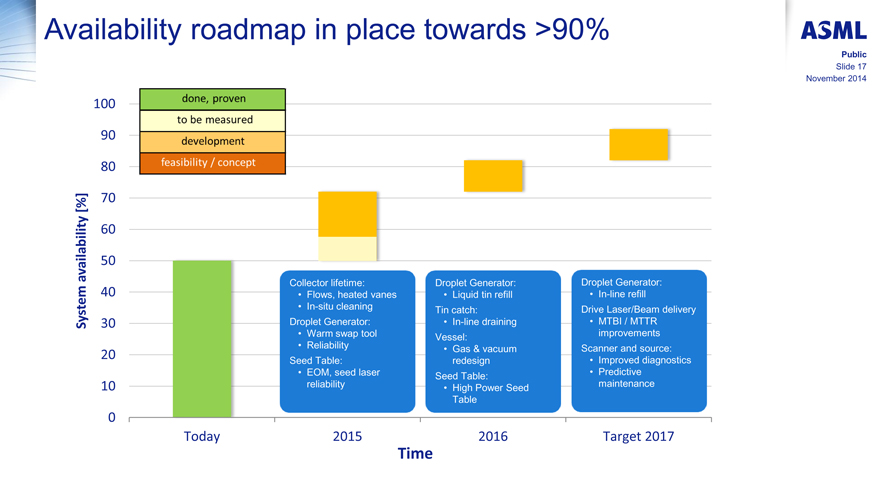

1 Delay in EUV insertion

Source power / availability not scaling up fast enough for HVM introduction

EUV infrastructure not ready in time

2 Competition and substitutes

Increased competition in DUV

Substitutes for EUV becoming technically feasible and cost effective

�

1 Even with delayed EUV delivery we will remain profitable and able to deliver significant value to our customers

ASML ASML Public Slide 15 November 2014

Delay in EUV insertion

Source power / availability not scaling up fast enough for HVM introduction

EUV infrastructure not ready on time

ASML approach

We have allocated massive resources to deliver our EUV roadmap (incl. acquisition Cymer) to maintain our customer�s roadmap

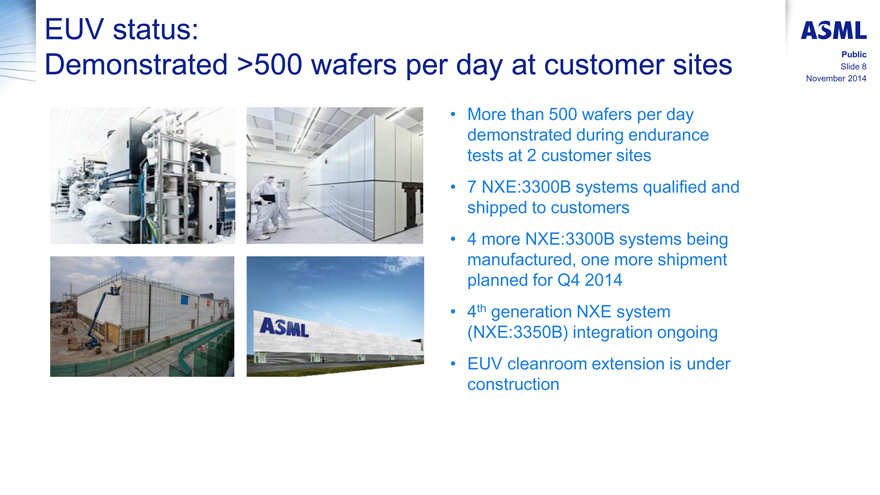

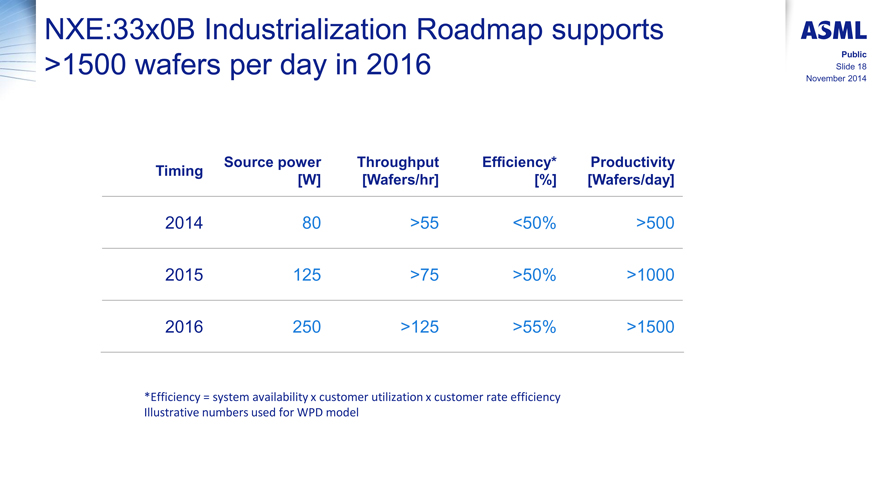

Customers indicated, EUV will be introduced when we meet a reliable 500 wafer per day threshold (which we expect to realize soon)

Economics of Moore�s law still hold in an 80W EUV world, with 35% instead of 41% node-on-node cost decline

The financial downside of potential later EUV adoption is mitigated by additional DUV demand

We continuously monitor progress on EUV enablers (resist, mask, etc.) and evaluate where our action would be needed

�

2 We remain competitive in DUV and watch potential EUV substitutions

ASML Public Slide 16 November 2014

Competition and substitutes

Increased competition in DUV

Substitutes for EUV becoming cost effective (Multiple patterning and Non-photo-litho technologies)

ASML approach

We continue executing our DUV and Apps roadmaps and make material R&D commitments and therefore we will maintain our competitive position as holistic Litho solution provider

Multiple patterning

Next to cost, we believe EUV is more attractive than multiple patterning because of reduced complexity resulting in better yield, yield ramp-up and fab cycle time

Additional DUV demand will mitigate the risk of multiple patterning substitution

Alternative technologies

Currently there are no viable alternatives at scale. DSA (direct self assembly) is not an alternative, but a complementary to Litho

We continuously monitor progress and status of alternative technologies

�

Summary: ASML�s positioning, opportunities and threats

ASML Public Slide 17 November 2014

ASML�s prime responsibility is to provide value for our customers, shareholders, employees, and supply chain partners

Our success is based on delivering Litho products with superior performance at lowest cost of ownership and on our flexible operating model required for an inherently volatile market

ASML models an annual total revenue opportunity of 10B€ by 2020 and subsequent growth beyond

We have reviewed our most impactful threats and feel confident about our approach to mitigate these

�

ASML

INVESTOR DAY

ASMLSMALLTALK2014

LONDON

Exhibit 99.3

�

�

ASML

Many ways to shrink:

The right moves to 10 nanometer and beyond

Martin van den Brink

President�& Chief Technology Officer

24�November 2014

INVESTOR DAY

ASMLSMALLTALK2014

LONDON

�

Forward looking statements

ASML

Public

Slide 2

November 2014

This document contains statements relating to certain projections and business trends that are forward-looking, including statements with respect to our outlook, expected customer demand in specified market segments, expected sales levels and trends, our market share, customer orders and systems backlog, IC unit demand, expected or indicative financial results or targets, including revenue, gross margin, expenses, gross margin percentage, opex percentage of sales, tax percentage, cash conversion cycle, capex percentage of sales, credit rating and earnings per share, expected shipments of tools and the timing thereof, including expected shipments of EUV and DUV tools, productivity of our tools and systems performance, including EUV system performance (such as endurance tests), the development of EUV technology and timing of shipments, development in IC technology, including shrink scenarios, NAND technology development and cost estimates, expectations on development of the shrink roadmap across all of our systems, upgradeability of our tools, system orders, customer transition estimates, expected transition scaling, forecasted industry developments, including expected smartphone, tablet and server use in future years, and expectations relating to new applications including wearable devices and connected devices, expected investment pay-back time for foundries, expected construction of additional holistic lithography infrastructure, the continuation of Moore�s Law, and our dividend policy and intention to repurchase shares. You can generally identify these statements by the use of words like �may�, �will�, �could�, �should�, �project�, �believe�, �anticipate�, �expect�, �plan�, �estimate�, �forecast�, �potential�, �intend�, �continue� and variations of these words or comparable words. These statements are not historical facts, but rather are based on current expectations, estimates, assumptions and projections about the business and our future financial results and readers should not place undue reliance on them.

Forward-looking statements do not guarantee future performance and involve risks and uncertainties. These risks and uncertainties include, without limitation, economic conditions, product demand and semiconductor equipment industry capacity, worldwide demand and manufacturing capacity utilization for semiconductors (the principal product of our customer base), the impact of general economic conditions on consumer confidence and demand for our customers� products, competitive products and pricing, affordability of shrink, the continuation of Moore�s Law, the impact of manufacturing efficiencies and capacity constraints, performance of our systems, the continuing success of technology advances and the related pace of new product development and customer acceptance of new products and customers meeting their own development roadmaps, market demand for our existing products and for new products and our ability to maintain or increase or market share, the development of and customer demand for multi-patterning technology and our ability to meet overlay and patterning requirements, the number and timing of EUV systems expected to be shipped, our ability to enforce patents and protect intellectual property rights, the risk of intellectual property litigation, EUV system performance and customer acceptance, availability of raw materials and critical manufacturing equipment, trade environment, our ability to reduce costs, changes in exchange rates and tax rates, available cash, distributable reserves for dividend payments and share repurchases, changes in our treasury policy, including our dividend and repurchase policy, completion of sales orders, the risk that key assumptions underlying financial targets prove inaccurate, including assumptions relating to market share, lithography market growth and our customers� ability to reduce productions costs, risks associated with Cymer, which we acquired in 2013, and other risks indicated in the risk factors included in ASML�s Annual Report on Form 20-F and other filings with the US Securities and Exchange Commission. These forward-looking statements are made only as of the date of this document. We do not undertake to update or revise the forward-looking statements, whether as a result of new information, future events or otherwise.

�

ASML

Public

Slide 3

November 2014

Content

Industry Challenges

The desire to shrink

The device challenges

The scaling challenges

ASML Solutions

Our holistic approach to extend immersion

The process simplification by using EUV

�

Moore�s Law: the rice-and-chessboard challenge

The benefits of shrink are irresistible

ASML

Public

Slide 4

November 2014

�

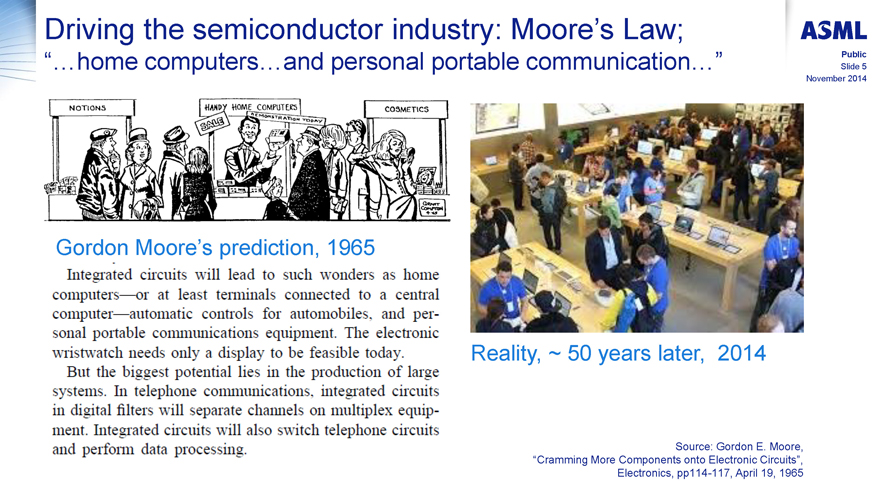

Driving the semiconductor industry: Moore�s Law;

�...home computers... and personal portable communication...�

ASML

Public

Slide 5

November 2014

Gordon Moore�s prediction, 1965

Integrated circuits will lead to such wonders as home computers�or at least terminals connected to a central computer�automatic controls for automobiles, and personal portable communications equipment. The electronic wristwatch needs only a display to be feasible today.

But the biggest potential lies in the production of large systems. In telephone communications, integrated circuits in digital filters will separate channels on multiplex equipment. Integrated circuits will also switch telephone circuits and perform data processing.

Reality, ~ 50 years later, 2014

Source: Gordon E. Moore,

�Cramming More Components onto Electronic Circuits�,

Electronics, pp114-117,�April�19, 1965

�

Some question if Moore�s Law can continue

ASML

Public

Slide 6

November 2014

C|net Search CNET

End of Moore�s Law: It�s not

about physics

A DARPA director argues that the end of the Moore�s law � which why you now have a tablet in your hand � could come about bec insurmountable economic challenges

by Brooke Crothers @mbrookec August�28, 2013 6:15 AM PDT

ZDNet

Hot Topics

Reviews

Downloads

Newsletters

White Papers

Moore�s Law: the end is near

PCWorld

Work, Life productivity

Seeking Alpha

Read. Decide. Invest.

Intel: The End of Moore�s

OK, OK, so we are not yet at the end of Moo

end from here.

Moore�s law comes to us from Gordon Moore

Semiconductor (FCS) and, later, Intel Corpo

Moore wrote a paper in 1965 describing his transistors on a given cost integrated circuit invention of the integrated circuit, and his transistor would continue to double, at the foreseeable future. The subtle detail discussions of Moore�s law is that the SAME COST. So the size of a transistor has less expensive.

Cost per Million Gates ($)

.0450

.0400

.0350

.0300

.0250

.0200

.0150

.0100

.0050

.0000

.0401

90nm

.0282

65nm

.0194

40nm

.0140

28nm

.0142

20nm

.0162

16/14nm

�

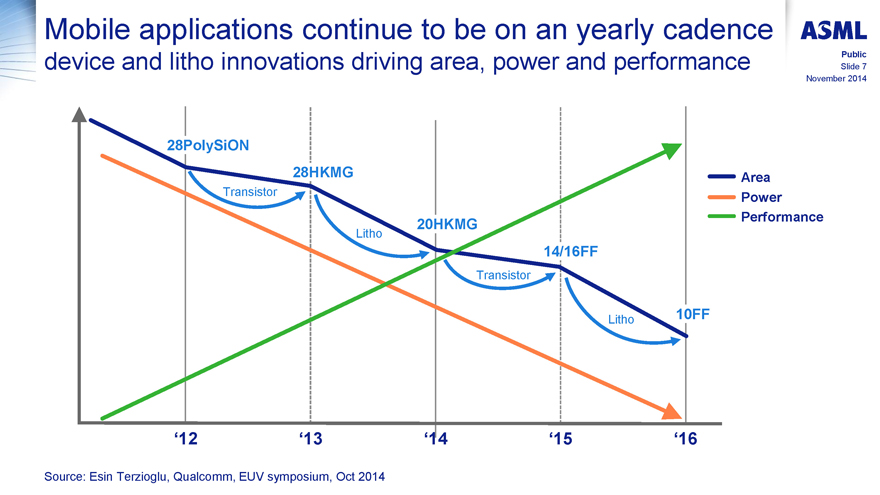

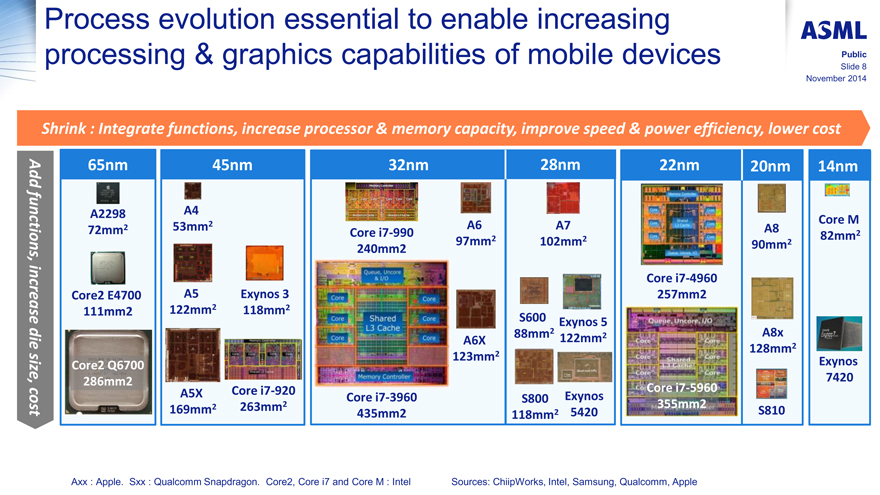

Mobile applications continue to be on an yearly cadence device and litho innovations driving area, power and performance

ASML

Public

Slide 7

November 2014

28PolySiON

28HKMG Area

Transistor Power

20HKMG Performance

Litho

14/16FF

Transistor

Litho 10FF

�12 �13 �14 �15 �16

Source: Esin Terzioglu, Qualcomm, EUV symposium, Oct 2014

�

Mobile chips integrating functionality faster than shrink

Apple: first high volume 20nm process in the iPhone 6(+)

ASML

Public

Slide 8

November 2014

Add Functionality

Add Functionality

IC Shrink 41%

Add Functionality

Add Functionality

Apple A6x

New Dual Core and 4-GPU needed for Retina Display iPad 4 123 mm2 - 32 nm

IC Shrink 15% and added 64bit

Apple A4 1-Core and 1-GPU 53 mm2 - 45 nm

Apple A5 2-Core and 2GPU needed for iPad Display 122 mm2 � 45 nm

Apple A5X - iPad 3 2-Core and 4-GPU needed for Retina Display 169 mm2 - 45 nm

Apple A5S � Apple TV, iPad2, iPad Mini, ipod Touch 70 mm2 - 32nm

De-featuring

Apple A5_3 - Apple TV Single Core, 2-GPU 38 mm2 - 32 nm

Apple A7 - iPhone 5S�& iPad Air Two 64bit cores 1 Billion transistors 102 mm2 - 28 nm Apple

IC Shrink 12%

45nm

32nm

28nm

20nm

Source: Apple

�

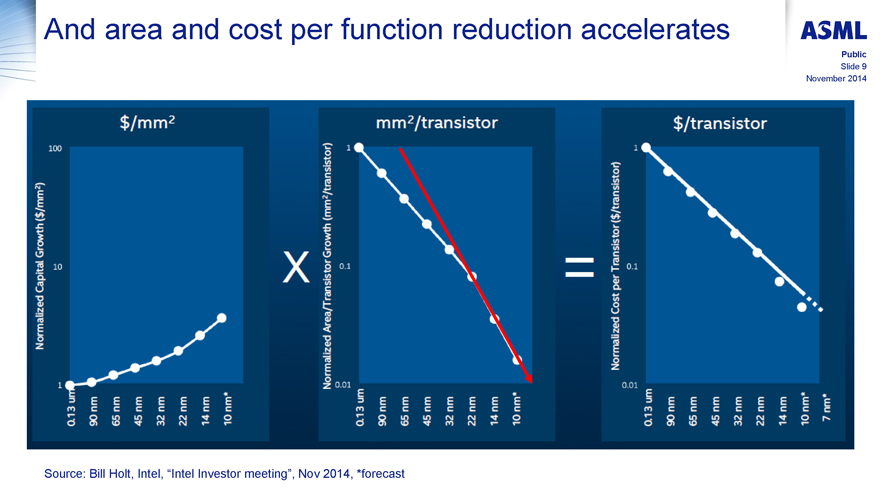

And area and cost per function reduction accelerates

ASML

Public

Slide 9�November 2014

$/mm2

Normalized Capital Growth ($/mm2)

100

10

1

0.13 um

90 nm

65 nm

45 nm

32 nm

22 nm

14 nm

10 nm*

X

mm2/transistor

Normalized Area/Transistor Growth (mm2/transistor)

1

0.1

0.01

0.13 um

90 nm

65 nm

45 nm

32 nm

22 nm

14 nm

10 nm*

=

$/transistor

Normalized Cost per Transistor ($/transistor)

1

0.1

0.01

0.13 um

90 nm

65 nm

45 nm

32 nm

22 nm

14 nm

10 nm*

7 nm*

Source: Bill Holt, Intel, �Intel Investor meeting�, Nov 2014, *forecast

�

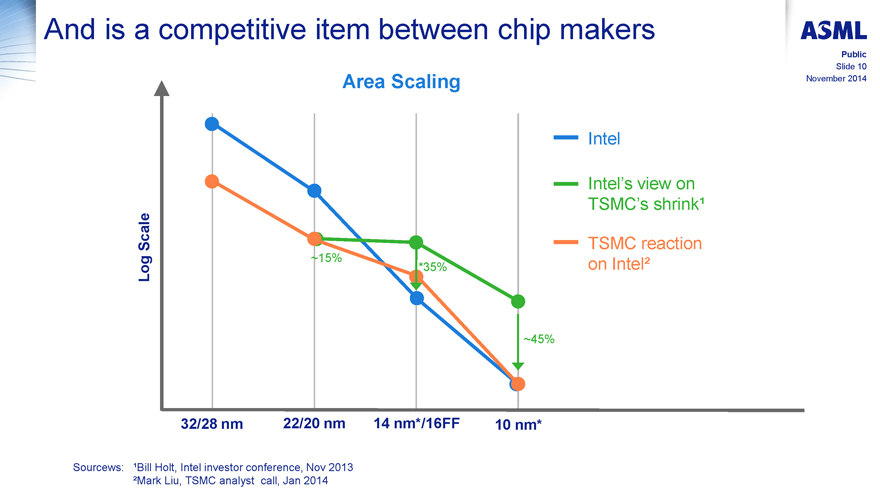

And is a competitive item between chip makers

ASML

Public

Slide 10

November 2014

Area Scaling

Log Scale

~15%

*35%

~45%

Intel

Intel�s view on TSMC�s shrink1

TSMC reaction on Intel2

32/28 nm 22/20 nm 14 nm*/16FF 10 nm*

Sourcews:

1Bill Holt, Intel investor conference, Nov 2013

2Mark Liu, TSMC analyst call, Jan 2014

�

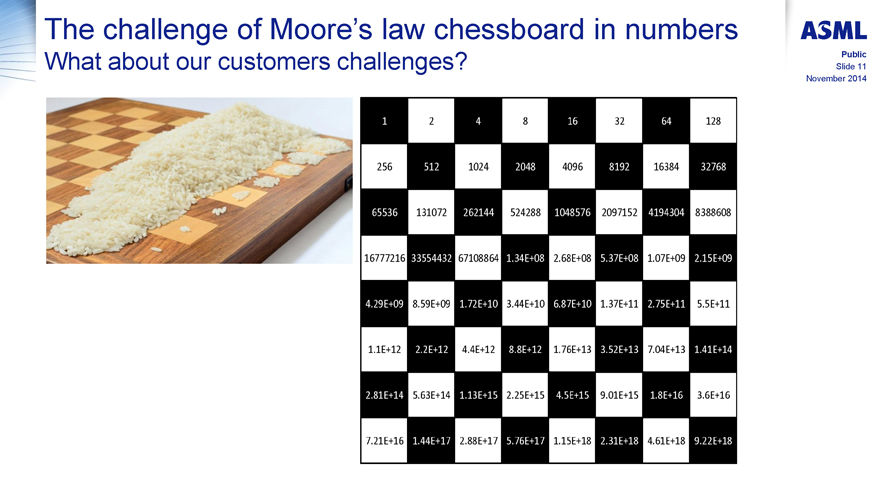

The challenge of Moore�s law chessboard in numbers

What about our customers challenges?

ASML

Public

Slide 11

November 2014

1 2 4 8 16 32 64 128

256 512 1024 2048 4096 8192 16384 32768

65536 131072 262144 524288 1048576 2097152 4194304 8388608

16777216 33554432 67108864 1.34E+08 5.37E+08 1.07E+09 2.15E+09

4.29E+09 8.59E+09 1.72E+10 3.44E+10 6.87E+10 1.37E+11 2.75E+11 5.5E+11

1.1E+12 2.2E+12 4.4E+12 8.8E+12 1.76E+13 3.52E+13 7.04E+13 1.41E+14

2.81E+14 5.63E+14 1.13E+15 2.2E+15 4.5E+15 9.01E+15 1.8E+16 3.6E+16

7.21E+16 1.44E+17 2.88E+17 5.76E+17 1.15E+18 2.31E+18 4.61E+18 9.22E+18

�

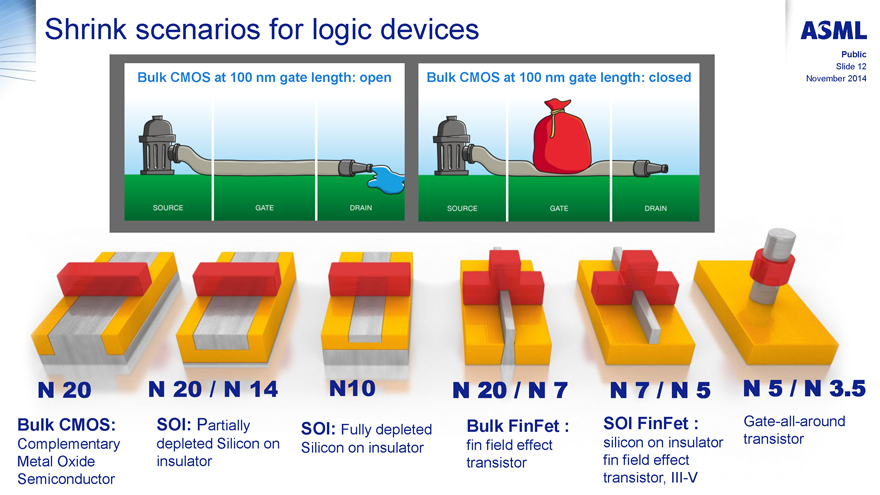

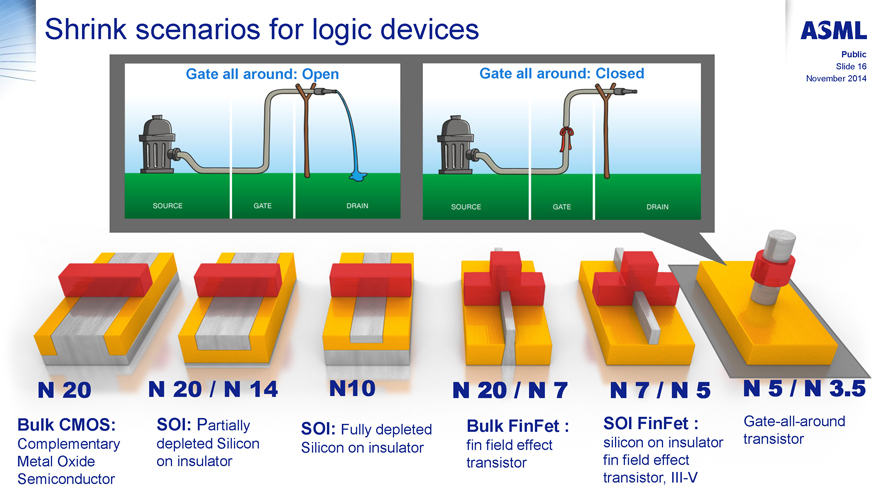

Shrink scenarios for logic devices

ASML

Public

Slide 12

November 2014

Bulk CMOS at 100 nm gate length: open

SOURCE GATE DRAIN

Bulk CMOS at 100 nm gate length: closed

SOURCE GATE DRAIN

N 20

Bulk CMOS:

Complementary Metal Oxide Semiconductor

N 20 / N 14

SOI: Partially depleted Silicon on insulator

N10

SOI: Fully depleted Silicon on insulator

N 20 / N 7

Bulk FinFet :

fin field effect transistor

N 7 / N 5

SOI FinFet :

silicon on insulator fin field effect transistor, III-V

N 5 / N 3.5

Gate-all-around transistor

�

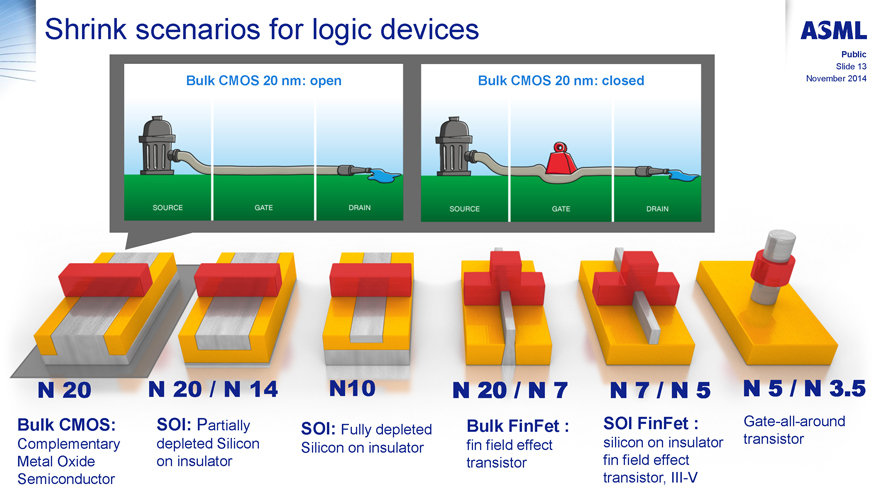

Shrink scenarios for logic devices

ASML

Public

Slide 13

November 2014

Bulk CMOS 20 nm: open

SOURCE GATE DRAIN

Bulk CMOS 20 nm: closed

SOURCE GATE DRAIN

N 20

Bulk CMOS:

Complementary Metal Oxide Semiconductor

N 20 / N 14

SOI: Partially depleted Silicon on insulator

N10

SOI: Fully depleted Silicon on insulator

N 20 / N 7

Bulk FinFet :

fin field effect transistor

N 7 / N 5

SOI FinFet :

silicon on insulator fin field effect transistor, III-V

N 5 / N 3.5

Gate-all-around transistor

�

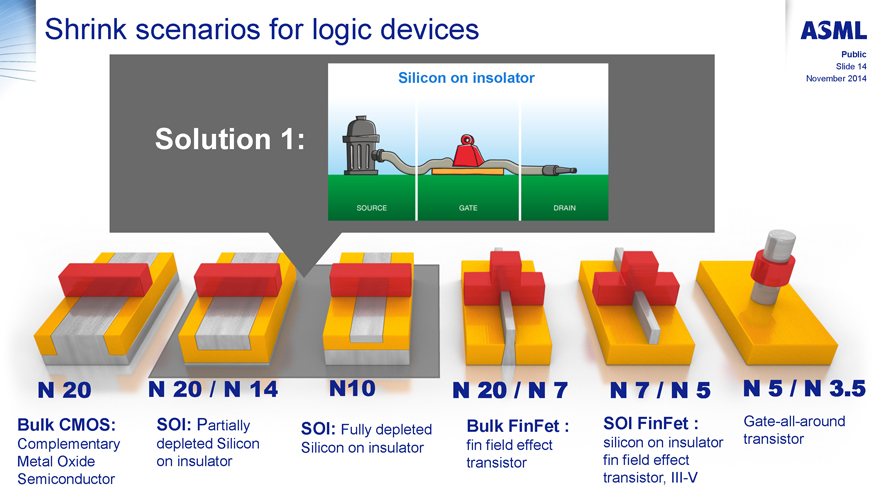

Shrink scenarios for logic devices

ASML

Public

Slide 14

November 2014

Solution 1:

Silicon on insolator

SOURCE GATE DRAIN

N 20

Bulk CMOS:

Complementary Metal Oxide Semiconductor

N 20 / N 14

SOI: Partially depleted Silicon on insulator

N10

SOI: Fully depleted Silicon on insulator

N 20 / N 7

Bulk FinFet :

fin field effect transistor

N 7 / N 5

SOI FinFet :

silicon on insulator fin field effect transistor, III-V

N 5 / N 3.5

Gate-all-around transistor

�

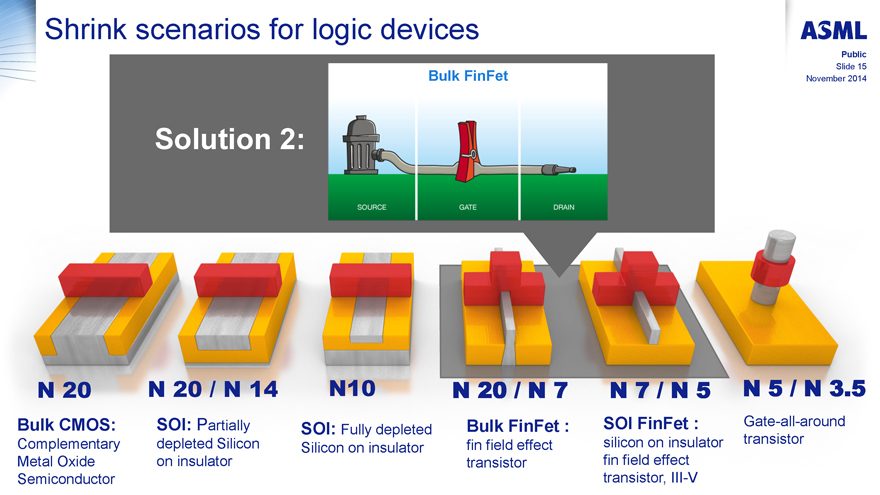

Shrink scenarios for logic devices

ASML

Public

Slide 15

November 2014

Solution 2:

Bulk FinFet

SOURCE GATE DRAIN

N 20

Bulk CMOS:

Complementary Metal Oxide Semiconductor

N 20 / N 14

SOI: Partially depleted Silicon on insulator

N10

SOI: Fully depleted Silicon on insulator

N 20 / N 7

Bulk FinFet :

fin field effect transistor

N 7 / N 5

SOI FinFet :

silicon on insulator fin field effect transistor, III-V

N 5 / N 3.5

Gate-all-around transistor

�

Shrink scenarios for logic devices

ASML

Public

Slide 16

November 2014

Gate all around: Open

SOURCE GATE DRAIN

Gate all around: Closed

SOURCE GATE DRAIN

N 20

Bulk CMOS:

Complementary Metal Oxide Semiconductor

N 20 / N 14

SOI: Partially depleted Silicon on insulator

N10

SOI: Fully depleted Silicon on insulator

N 20 / N 7

Bulk FinFet :

fin field effect transistor

N 7 / N 5

SOI FinFet :

silicon on insulator fin field effect transistor, III-V

N 5 / N 3.5

Gate-all-around transistor

�

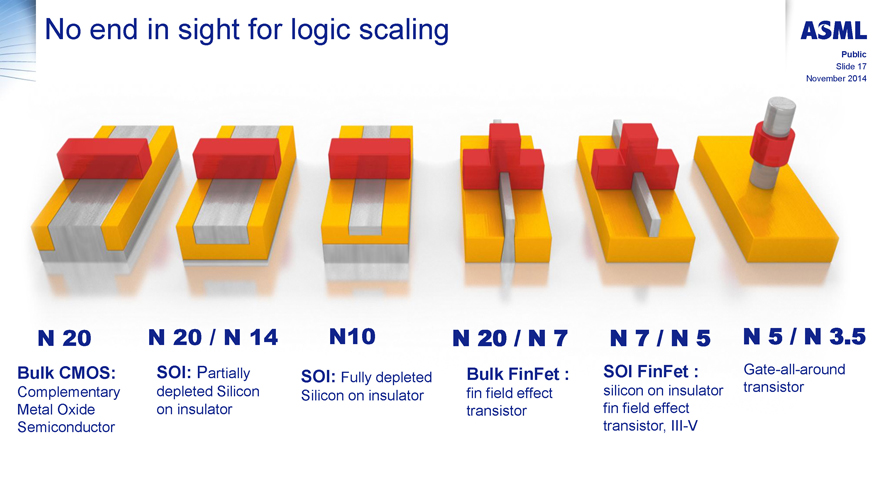

No end in sight for logic scaling

ASML

Public

Slide 17

November 2014

N 20

Bulk CMOS:

Complementary Metal Oxide Semiconductor

N 20 / N 14

SOI: Partially depleted Silicon on insulator

N10

SOI: Fully depleted Silicon on insulator

N 20 / N 7

Bulk FinFet :

fin field effect transistor

N 7 / N 5

SOI FinFet :

silicon on insulator fin field effect transistor, III-V

N 5 / N 3.5

Gate-all-around transistor

�

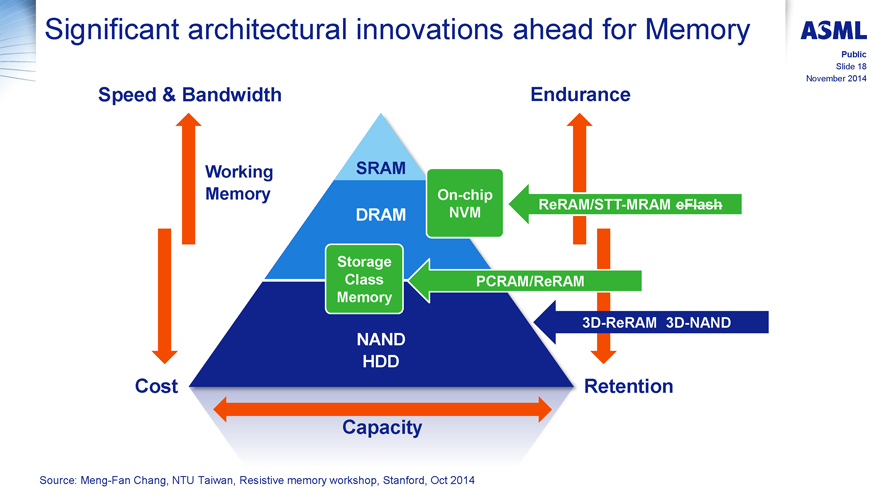

Significant architectural innovations ahead for Memory

ASML

Public

Slide 18

November 2014

Speed & Bandwidth

Working Memory

Cost

SRAM

DRAM

Storage Class Memory

NAND HDD

On-chip NVM

Endurance

ReRAM/STT-MRAM eFlash

PCRAM/ReRAM

3D-ReRAM 3D-NAND

Retention

Capacity

Source: Meng-Fan Chang, NTU Taiwan, Resistive memory workshop, Stanford, Oct 2014

�

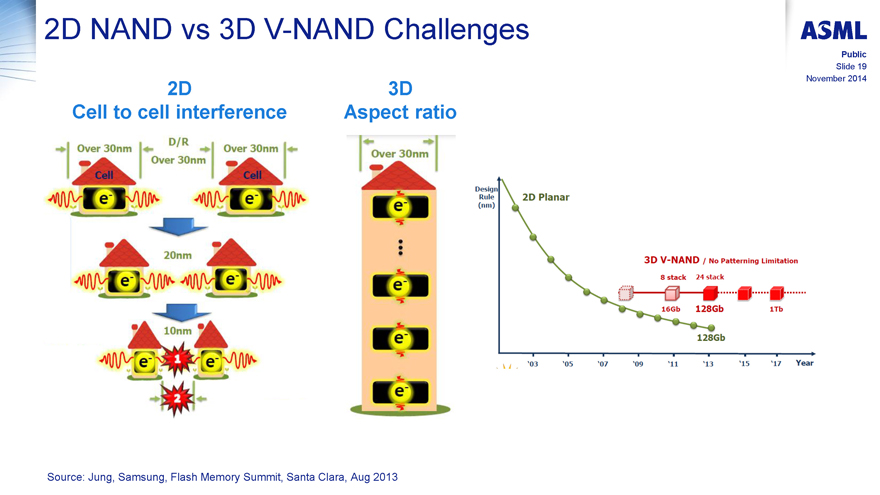

2D NAND vs 3D V-NAND Challenges

ASML

Public

Slide 19

November 2014

2D Cell to cell interference

Over 30nm D/R Over 30nm Over 30nm

Cell Cell

e- e-

20nm

e- e-

10nm

e- e-

1 2

3D Aspect ratio

Over 30nm

e-

e-

e-

e-

Design Rule (nm)

2D Planar

3D V-NAND / No Patterning Limitation

8 stack 24 stack

16Gb 128Gb 1Tb

128Gb

�03 �05 �07 �09 �11 �13 �15 �17 Year

Source: Jung, Samsung, Flash Memory Summit, Santa Clara, Aug 2013

�

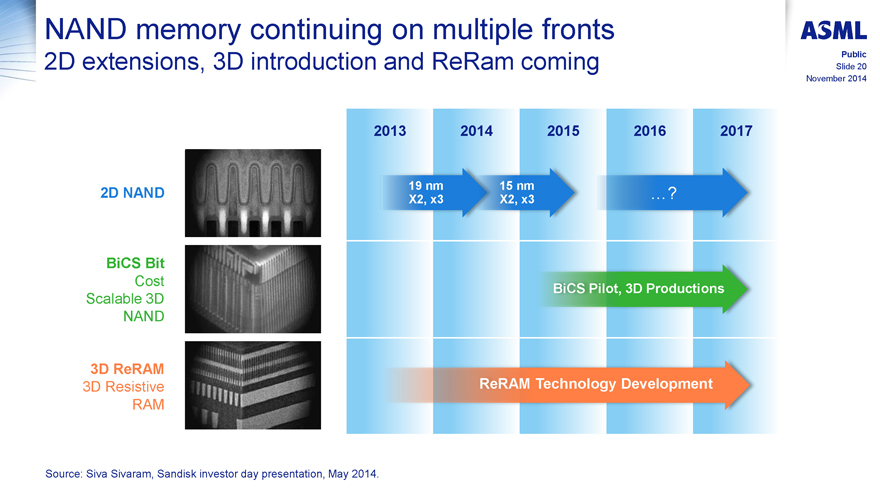

NAND memory continuing on multiple fronts

2D extensions, 3D introduction and ReRam coming

ASML

Public

Slide 20

November 2014

2D NAND

BiCS Bit

Cost

Scalable 3D

NAND

3D ReRAM

3D Resistive

RAM

2013 2014 2015 2016 2017

19 nm 15 nm �? X2, x3 X2, x3

BiCS Pilot, 3D Productions

ReRAM Technology Development

Source: Siva Sivaram, Sandisk investor day presentation, May 2014.

�

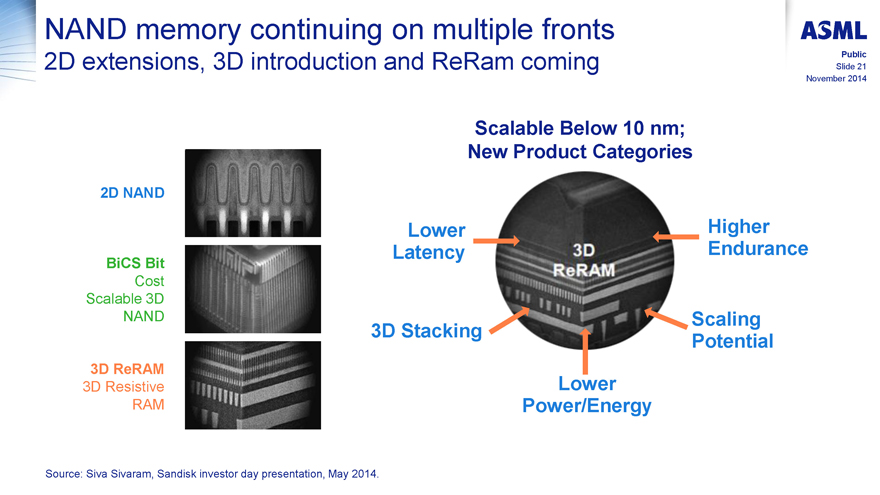

NAND memory continuing on multiple fronts

2D extensions, 3D introduction and ReRam coming

ASML

Public

Slide 21

November 2014

2D NAND

BiCS Bit

Cost

Scalable 3D

NAND

3D ReRAM

3D Resistive

RAM

Scalable Below 10 nm; New Product Categories

Lower Latency

3D Stacking

Lower Power/Energy

Scaling Potential

Higher Endurance

3D ReRAM

Source: Siva Sivaram, Sandisk investor day presentation, May 2014.

�

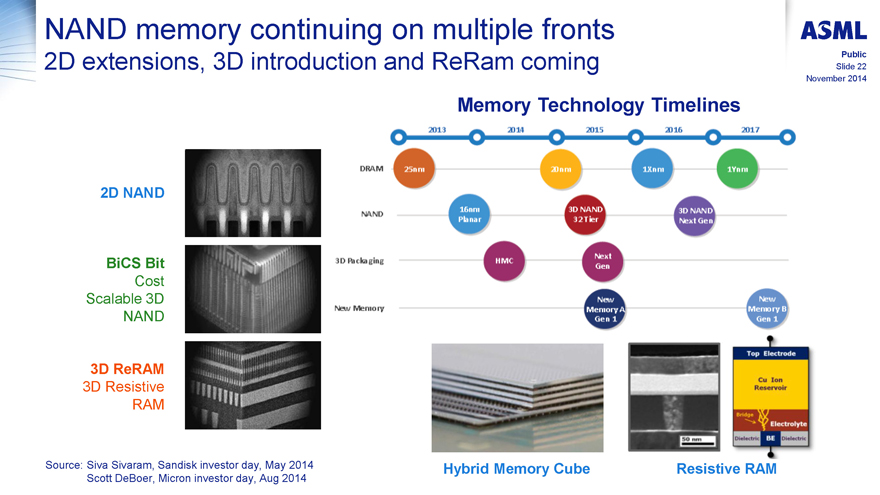

NAND memory continuing on multiple fronts

2D extensions, 3D introduction and ReRam coming

ASML

Public

Slide 22

November 2014

2D NAND

BiCS Bit

Cost

Scalable 3D

NAND

3D ReRAM

3D Resistive

RAM

Memory Technology Timelines

2013 2014 2015 2016 2017

DRAM 25nm 20nm 1Xnm 1Ynm

NAND 16nm Planar 3D NAND 32Tier 3D NAND Next Gen

3D Packaging HMC Next Gen

New Memory New Memory A Gen 1 New Memory B Gen 1

50 nm

Top Electrode

Cu Ion Reservoir

Bridge

Electrolyte

Dielectric BE Dielectric

Hybrid Memory Cube

Resistive RAM

Source: Siva Sivaram, Sandisk investor day, May 2014

Scott DeBoer, Micron investor day, Aug 2014

�

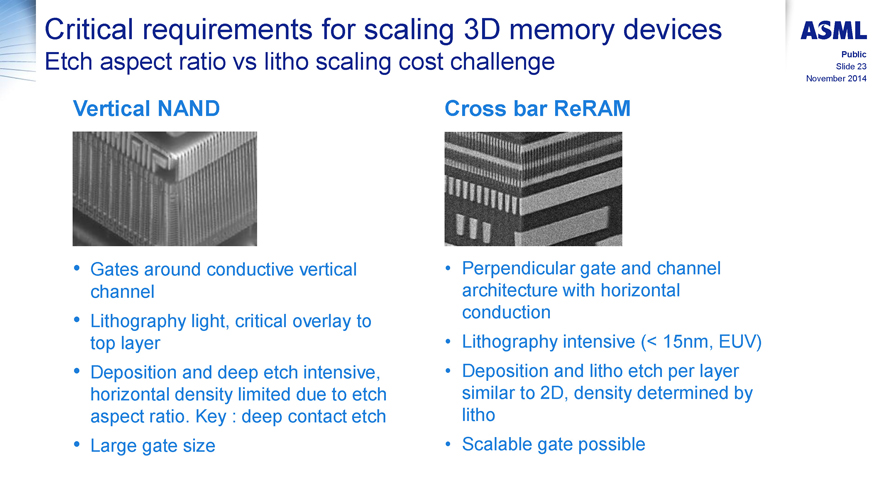

Critical requirements for scaling 3D memory devices

Etch aspect ratio vs litho scaling cost challenge

ASML

Public

Slide 23

November 2014

Vertical NAND

Gates around conductive vertical channel

Lithography light, critical overlay to top layer

Deposition and deep etch intensive, horizontal density limited due to etch aspect ratio. Key : deep contact etch

Large gate size

Cross bar ReRAM

Perpendicular gate and channel architecture with horizontal conduction

Lithography intensive (< 15nm, EUV)

Deposition and litho etch per layer similar to 2D, density determined by litho

Scalable gate possible

�

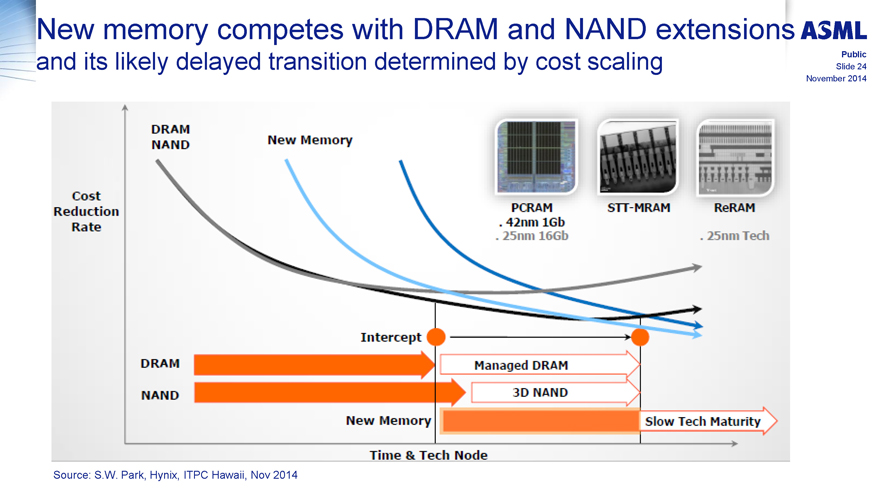

New memory competes with DRAM and NAND extensions

and its likely delayed transition determined by cost scaling

ASML

Public

Slide 24

November 2014

Cost Reduction Rate

DRAM NAND

New Memory

PCRAM . 42nm 1Gb . 25nm 16Gb

STT-MRAM

ReRAM . 25nm Tech

Intercept

DRAM Managed DRAM

NAND 3D NAND

New Memory Slow Tech Maturity

Time�& Tech Node

Source: S.W. Park, Hynix, ITPC Hawaii, Nov 2014

�

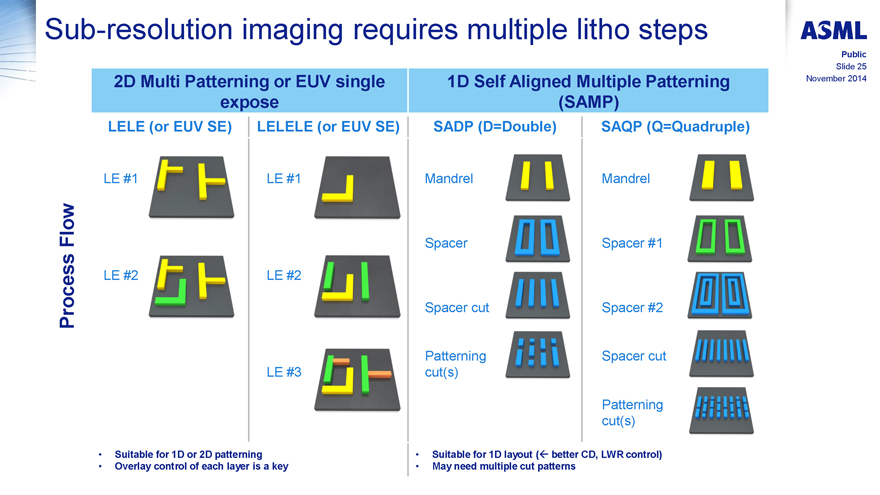

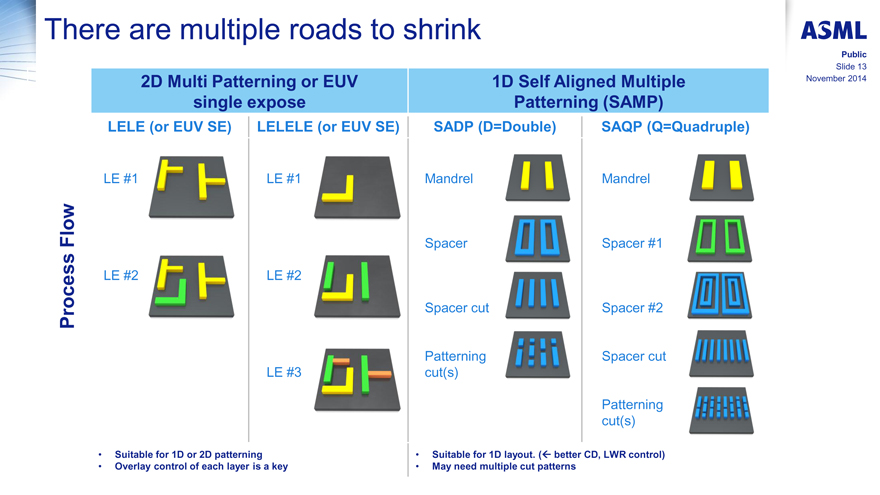

Sub-resolution imaging requires multiple litho steps

ASML

Public

Slide 25

November 2014

Process Flow

2D Multi Patterning or EUV single expose

LELE (or EUV SE)

LE #1 LE #2

LELELE (or EUV SE)

LE #1 LE #2 LE #3

1D Self Aligned Multiple Patterning (SAMP)

SADP (D=Double)

Mandrel

Spacer

Spacer cut

Patterning cut(s)

SAQP (Q=Quadruple)

Mandrel

Spacer #1

Spacer #2

Spacer cut

Patterning cut(s)

Suitable for 1D or 2D patterning

Overlay control of each layer is a key

Suitable for 1D layout ( better CD, LWR control)

May need multiple cut patterns

�

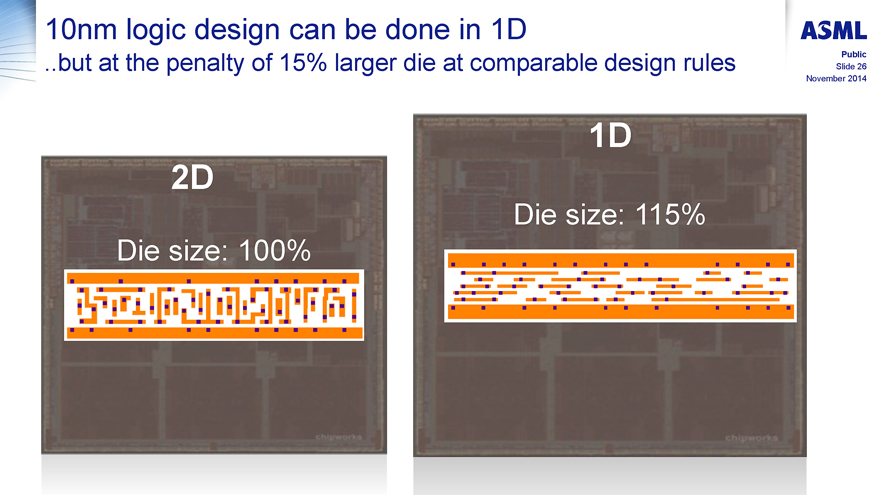

10nm logic design can be done in 1D

..but at the penalty of 15% larger die at comparable design rules

2D

Die size: 100%

1D

Die size: 115%

ASML

Public

Slide 26

November 2014

�

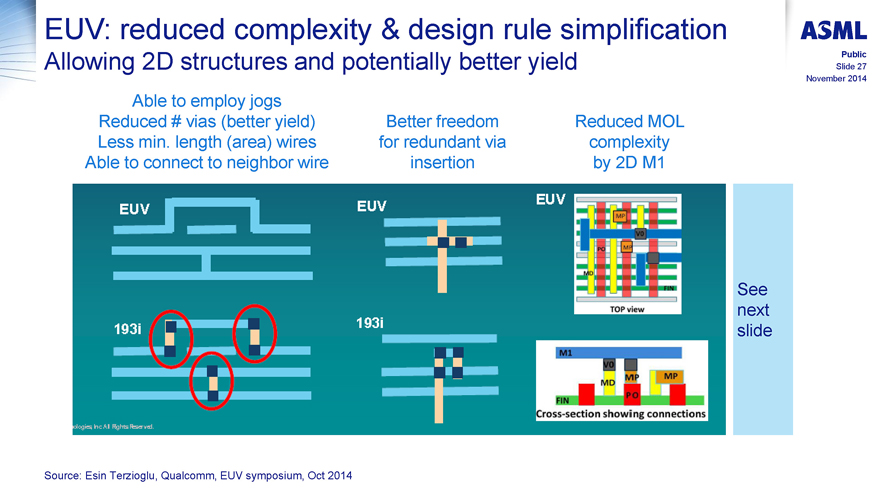

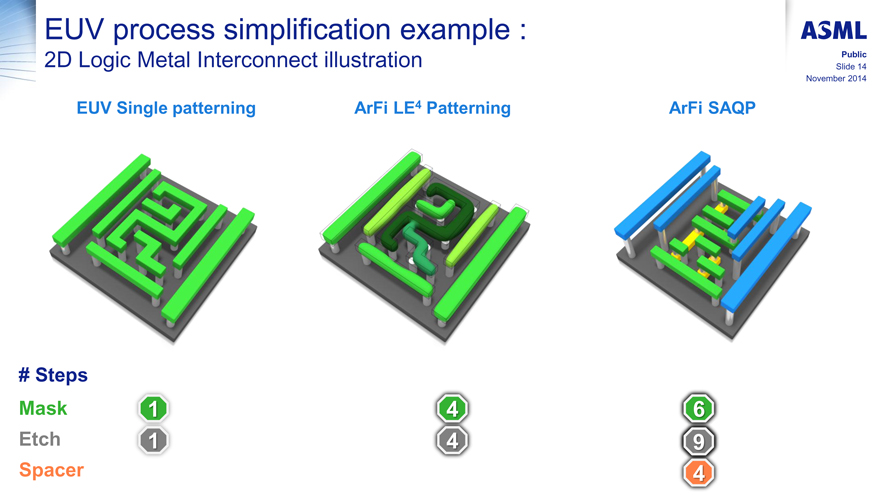

EUV: reduced complexity�& design rule simplification

Allowing 2D structures and potentially better yield

ASML

Public

Slide 27

November 2014

Able to employ jogs Reduced # vias (better yield) Less min. length (area) wires Able to connect to neighbor wire

Better freedom for redundant via insertion

Reduced MOL complexity by 2D M1

EUV

193i

EUV

193i

EUV

MP

V0

PO

MP

MD

TIN

TOP view

M1

V0

MD

MP

MP

FIN

PO

Cross-section showing connections

See next slide

Source: Esin Terzioglu, Qualcomm, EUV symposium, Oct 2014

�

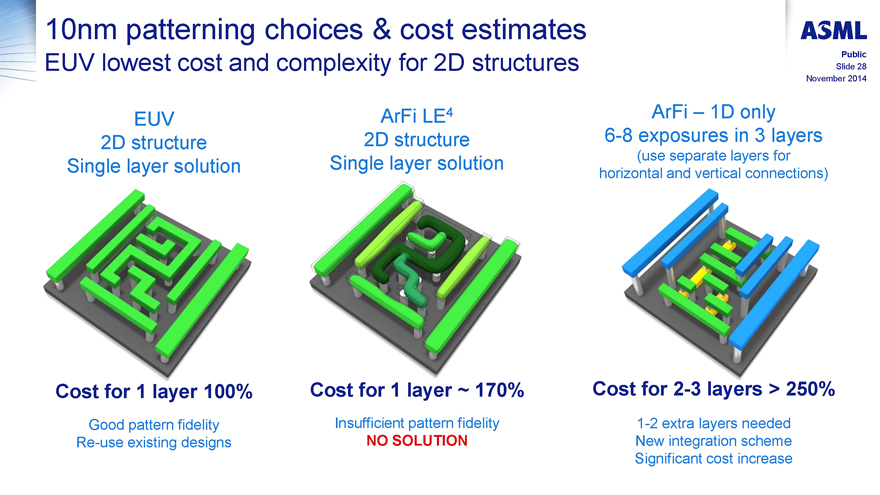

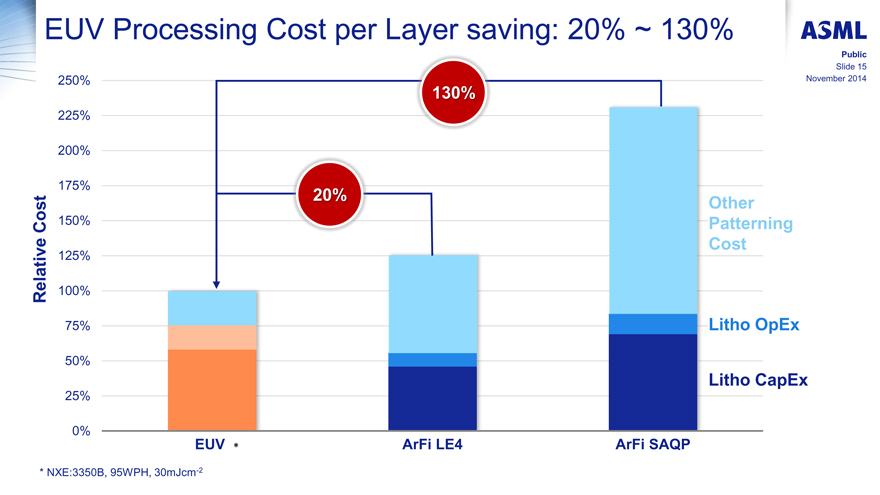

10nm patterning choices�& cost estimates

EUV lowest cost and complexity for 2D structures

ASML

Public

Slide 28

November 2014

EUV 2D structure Single layer solution

Cost for 1 layer 100%

Good pattern fidelity Re-use existing designs

ArFi LE4 2D structure Single layer solution

Cost for 1 layer ~ 170%

Insufficient pattern fidelity

NO SOLUTION

ArFi � 1D only 6-8 exposures in 3 layers (use separate layers for horizontal and vertical connections)

Cost for 2-3 layers > 250%

1-2 extra layers needed New integration scheme Significant cost increase

�

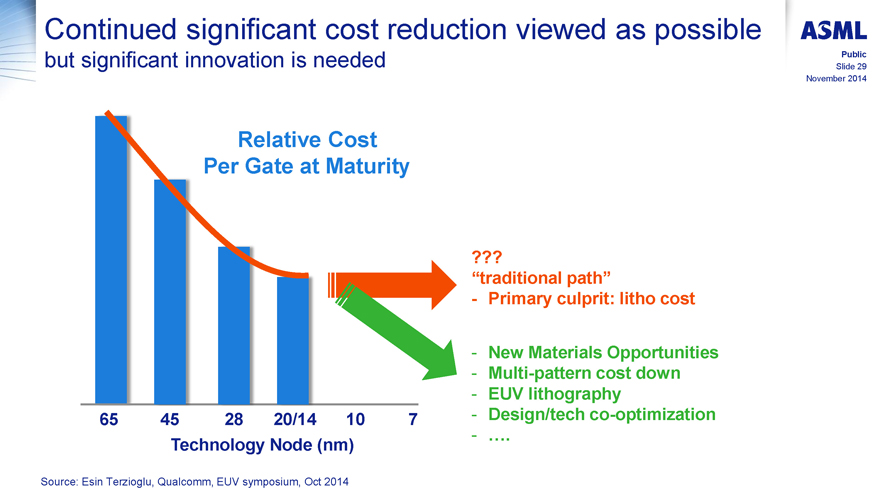

Continued significant cost reduction viewed as possible

but significant innovation is needed

ASML

Public

Slide 29

November 2014

Relative Cost Per Gate at Maturity

65 45 28 20/14 107

Technology Node (nm)

???

�traditional path�

- Primary culprit: litho cost

- New Materials Opportunities

- Multi-pattern cost down

- EUV lithography

- Design/tech co-optimization

- �.

Source: Esin Terzioglu, Qualcomm, EUV symposium, Oct 2014

�

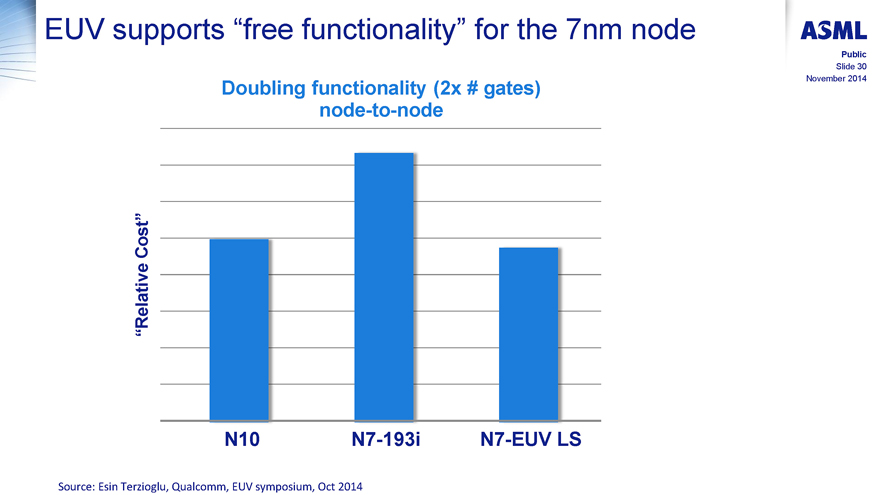

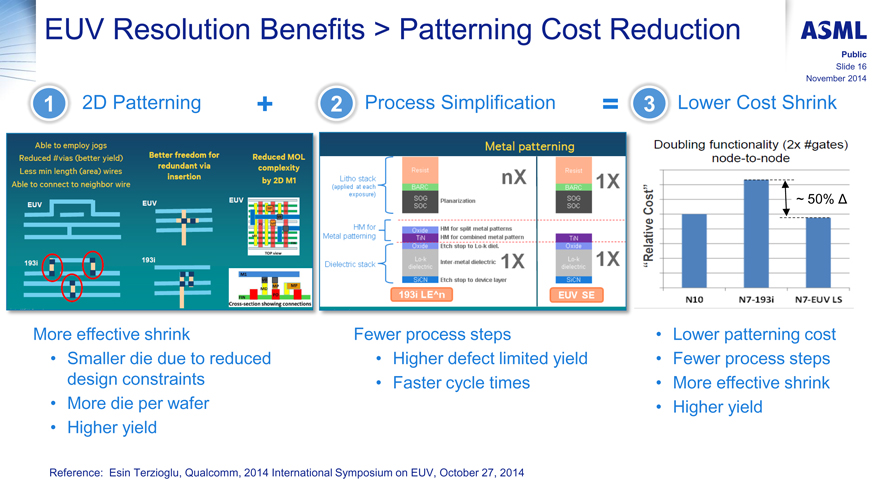

EUV supports �free functionality� for the 7nm node

ASML

Public

Slide 30

November 2014

Doubling functionality (2x # gates) node-to-node

�Relative Cost�

N10 N7-193i N7-EUV LS

Source: Esin Terzioglu, Qualcomm, EUV symposium, Oct 2014

�

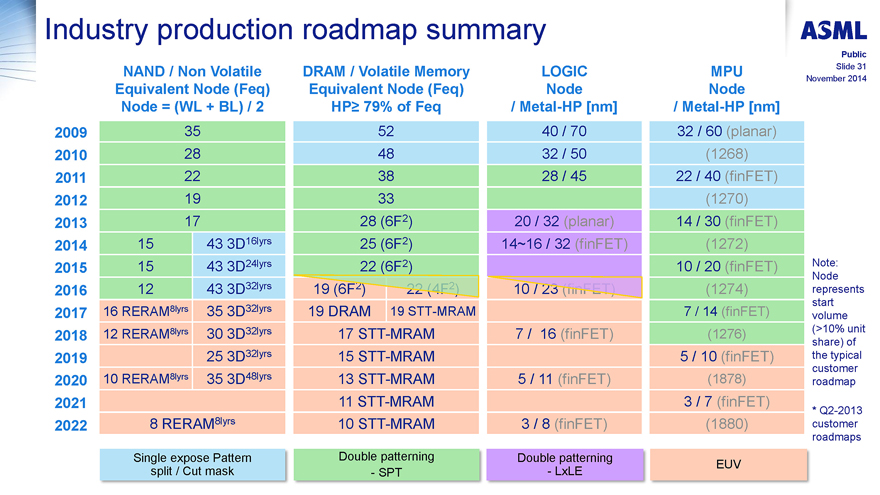

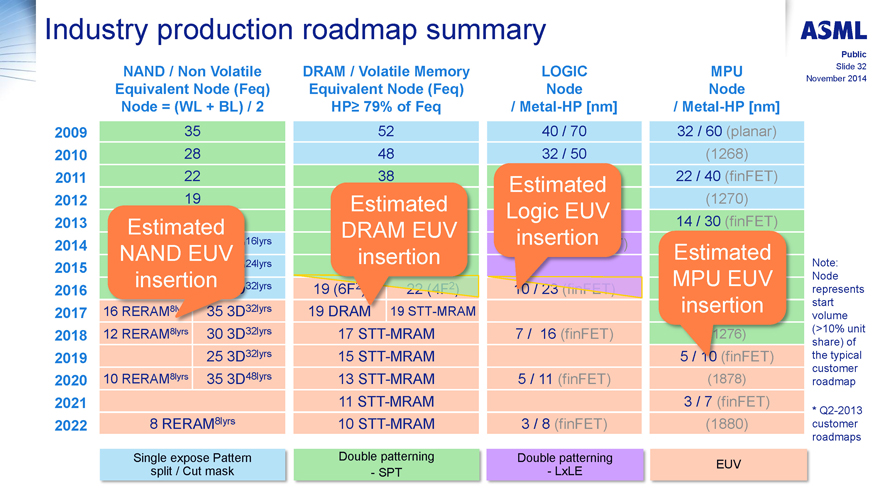

Industry production roadmap summary

ASML

Public

Slide 31

November 2014

NAND / Non Volatile Equivalent Node (Feq) Node = (WL + BL) / 2

DRAM / Volatile Memory Equivalent Node (Feq) HP� 79% of Feq

LOGIC Node / Metal-HP [nm]

MPU Node / Metal-HP [nm]

2009 35 52 40 / 70 32 / 60 (planar)

2010 28 48 32 / 50 (1268)

2011 22 38 28 / 45 22 / 40 (finFET)

2012 19 33 (1270)

2013 17 28 (6F2) 20 / 32 (planar) 14 / 30 (finFET)

2014 15 43 3D16lyrs 25 (6F2) 14~16 / 32 (finFET) (1272)

2015 15 43 3D24lyrs 22 (6F2) 10 / 20 (finFET)

2016 12 43 3D32lyrs 19 (6F2) 22 (4F2) 10 / 23 (finFET) (1274)

2017 16 RERAM8lyrs 35 3D32lyrs 19 DRAM 19 STT-MRAM 7 / 14 (finFET)

2018 12 RERAM8lyrs 30 3D32lyrs 17 STT-MRAM 7 / 16 (finFET) (1276)

2019 25 3D32lyrs 15 STT-MRAM 5 / 10 (finFET)

2020 10 RERAM8lyrs 35 3D48lyrs 13 STT-MRAM 5 / 11 (finFET) (1878)

2021 11 STT-MRAM 3 / 7 (finFET)

2022 8RERAM8lyrs 10 STT-MRAM 3 / 8 (finFET) (1880)

Single expose Pattern split / Cut mask

Double patterning - SPT

Double patterning - LxLE

EUV

Note: Node represents start volume (>10% unit share) of the typical customer roadmap

* Q2-2013 customer roadmaps

�

Industry production roadmap summary

ASML

Public

Slide 32

November 2014

NAND / Non Volatile Equivalent Node (Feq) Node = (WL + BL) / 2

DRAM / Volatile Memory Equivalent Node (Feq) HP� 79% of Feq

LOGIC Node / Metal-HP [nm]

MPU Node / Metal-HP [nm]

2009 35 52 40 / 70 32 / 60 (planar)

2010 28 48 32 / 50 (1268)

2011 22 38 22 / 40 (finFET)

2012 19 (1270)

2013 17 14 / 30 (finFET)

2014 16lyrs

2015 24lyrs

2016 32lyrs 19 (6F2) 22 (4F2) 10 / 23 (finFET)

2017 16 RERAM8lyrs 35 3D32lyrs 19 DRAM 19 STT-MRAM

2018 12 RERAM8lyrs 30 3D32lyrs 17 STT-MRAM 7 / 16 (finFET) (1276)

2019 25 3D32lyrs 15 STT-MRAM 5 / 10(finFET)

2020 10 RERAM8lyrs 35 3D48lyrs 13 STT-MRAM 5 / 11 (finFET) (1878)

2021 11 STT-MRAM 3 / 7 (finFET)

2022 8RERAM8lyrs 10 STT-MRAM 3 / 8 (finFET) (1880)

Single expose Pattern split / Cut mask

Double patterning - SPT

Double patterning - LxLE

EUV

Note: Node represents start volume (>10% unit share) of the typical customer roadmap

* Q2-2013 customer roadmaps

Estimated NAND EUV insertion

Estimated DRAM EUV insertion

Estimated Logic EUV insertion

Estimated MPU EUV insertion

�

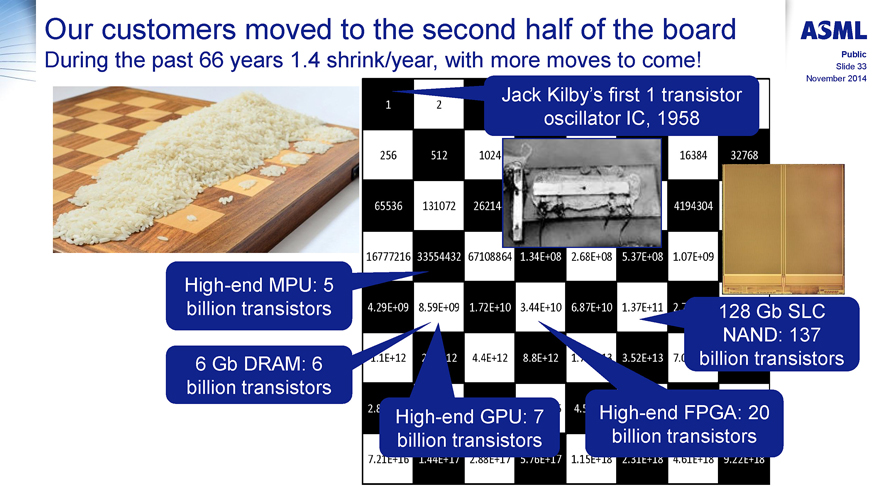

Our customers moved to the second half of the board

During the past 66 years 1.4 shrink/year, with more moves to come!

ASML

Public

Slide 33

November 2014

High-end MPU: 5 billion transistors

6 Gb DRAM: 6 billion transistors

Jack Kilby�s first 1 transistor oscillator IC, 1958

High-end GPU: 7 billion transistors

High-end FPGA: 20 billion transistors

128 Gb SLC NAND: 137 billion transistors

12

256 512 1024 16384 32768

65536 131072 26214 4194304

16777216 33554432 67108864 1.34E+08 2.68E+08 5.37E+08 1.07E+09

4.29E+09 8.59E+09 1.72E+10 3.44E+10 6.87E+10 1.37E+11 2.7

1.1E+12 12 4.4E+12 8.8E+12 1 3.52E+13 7.0

2.8 4.5

7.21E+16 1.44E+17 2.88E+17 5.76E+17 1.15E+18 2.31E+18 4.61E+18 9.22E+18

�

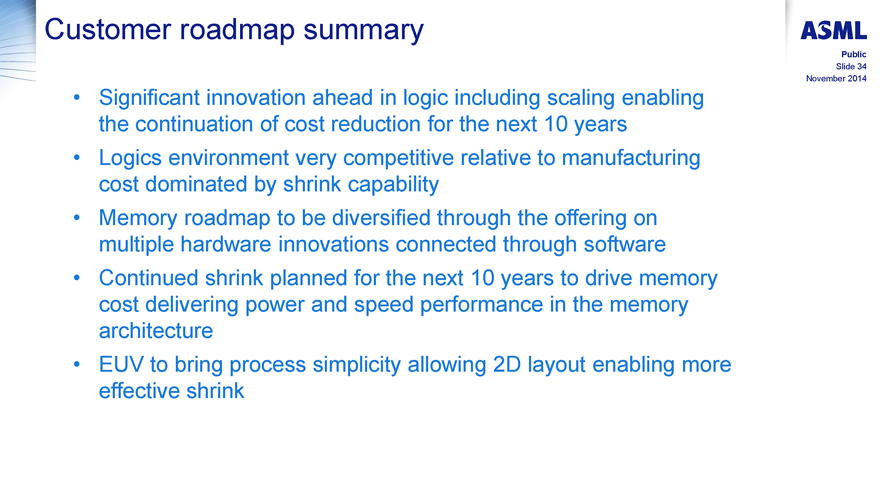

Customer roadmap summary

ASML

Public

Slide 34

November 2014

Significant innovation ahead in logic including scaling enabling the continuation of cost reduction for the next 10 years

Logics environment very competitive relative to manufacturing cost dominated by shrink capability

Memory roadmap to be diversified through the offering on multiple hardware innovations connected through software

Continued shrink planned for the next 10 years to drive memory cost delivering power and speed performance in the memory architecture

EUV to bring process simplicity allowing 2D layout enabling more effective shrink

�

ASML

Public

Slide 35

November 2014

Content

Industry Challenges

The desire to shrink

The device challenges

The scaling challenges

ASML Solutions

Our holistic approach to extend immersion

The process simplification by using EUV

�

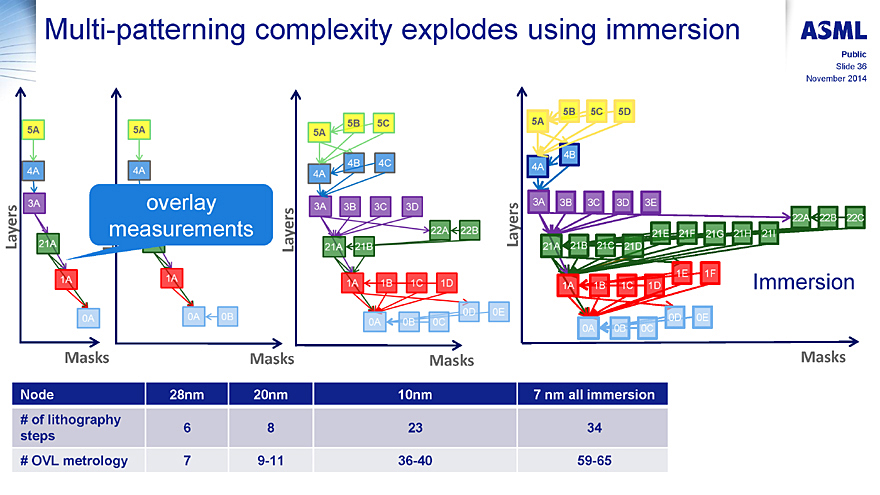

ASML

Public

Slide 36

November 2014

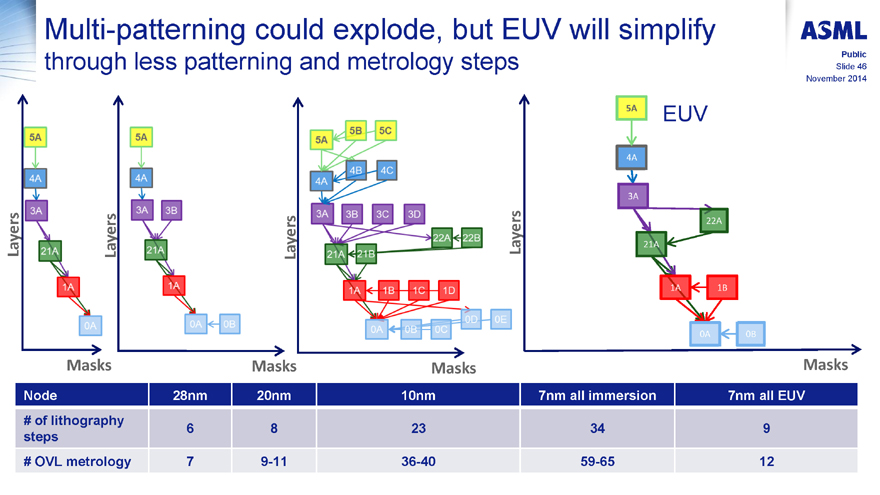

Multi-patterning complexity explodes using immersion

5A 5A 5A 5B 5C 5A 5B 5C 5D

4A 4A 4A 4B 4C 4A 4B

3A overlay measurements 3A 3B 3C 3D 3A 3B 3C 3D 3E

Layers 21A Layers 21A 21B 22A 22B

Layers 21A 21B 21C 21D 21E 21F 21G 21H 21I 22A 22B 22C

1A 1A 1A 1B 1C 1D 1A 1B 1C 1D 1E 1F Immersion

0A 0A 0B 0A 0B 0C 0D 0E 0A 0B 0C 0D 0E

Masks Masks Masks Masks

Node 28nm 20nm 10nm 7 nm all immersion

# of lithography steps 6 8 23 34

# OVL metrology 7 9-11 36-40 59-65

�

ASML

Public

Slide 37

November 2014

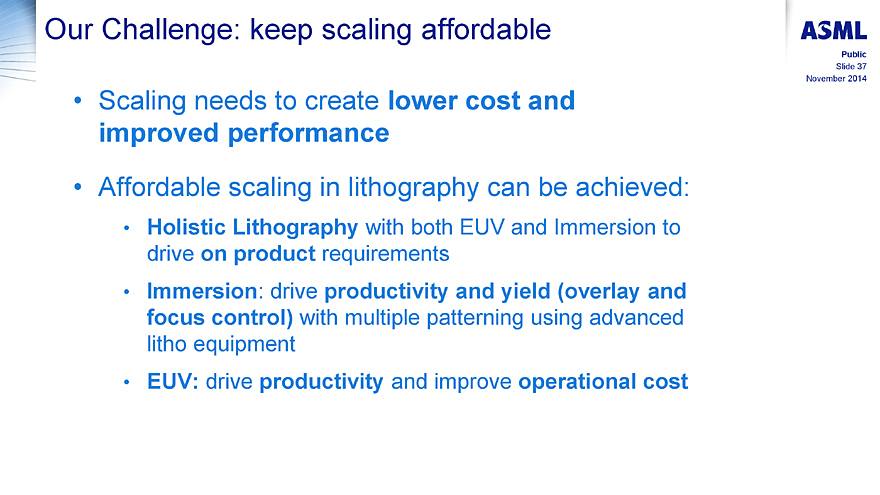

Our Challenge: keep scaling affordable

Scaling needs to create lower cost and improved performance

Affordable scaling in lithography can be achieved:

Holistic Lithography with both EUV and Immersion to drive on product requirements

Immersion: drive productivity and yield (overlay and focus control) with multiple patterning using advanced litho equipment

EUV: drive productivity and improve operational cost

�

ASML

Public

Slide 38

November 2014

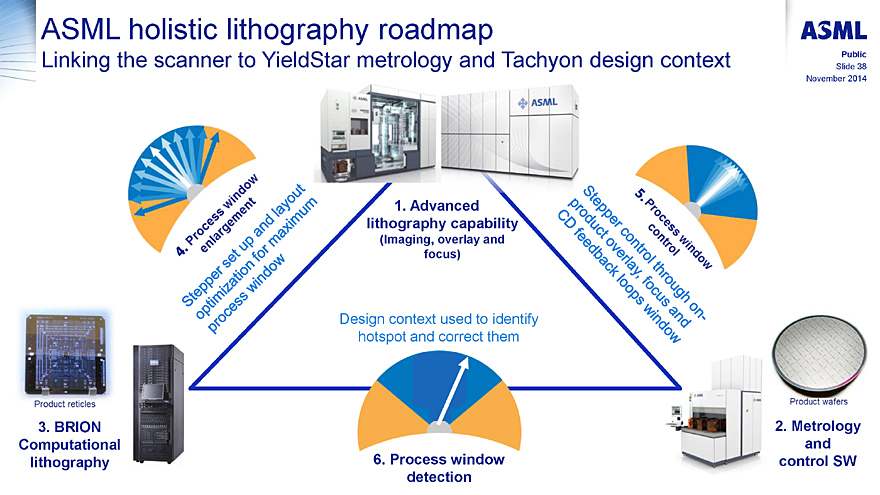

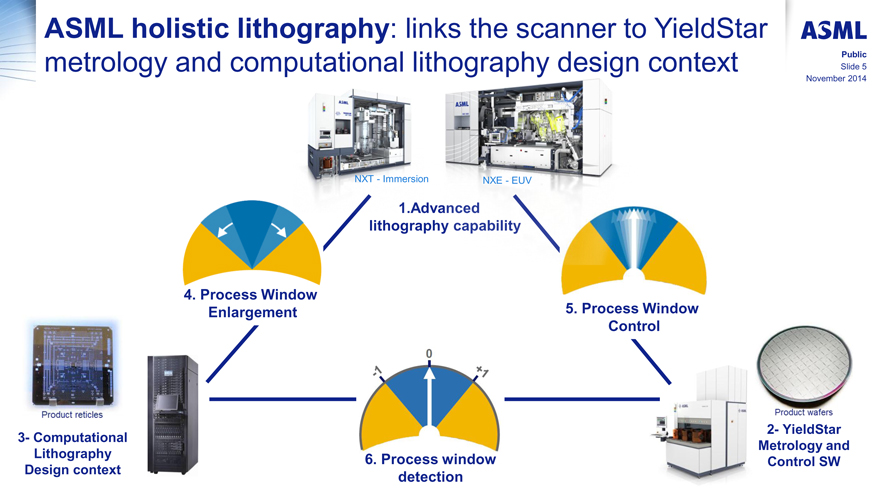

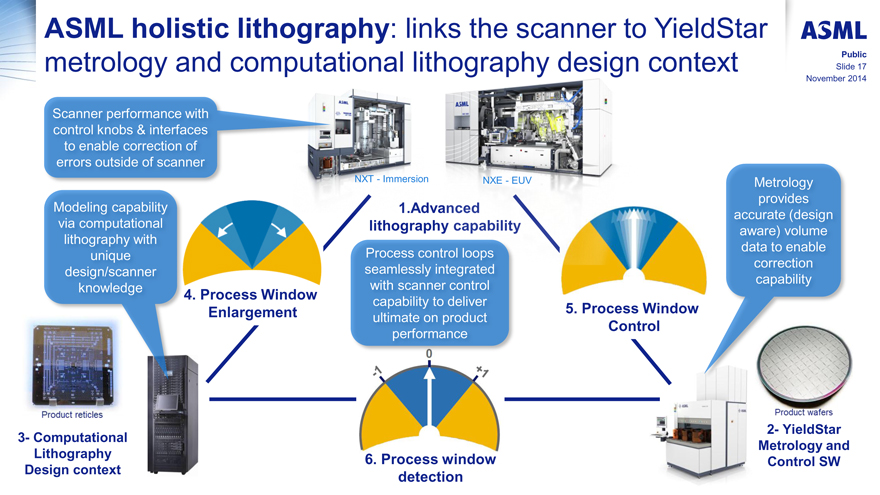

ASML holistic lithography roadmap

Linking the scanner to YieldStar metrology and Tachyon design context

4. Process window enlargement

Stepper set up and layout optimization for maximum process window

1. Advanced lithography capability (Imaging, overlay and focus)

5. Process window control

Stepper control through on-product overlay, focus and CD feedback loops window

Product reticles

Design context used to identify hotspot and correct them

Product wafers

3. BRION Computational lithography

6. Process window detection

2. Metrology and control SW

�

ASML

Public

Slide 39

November 2014

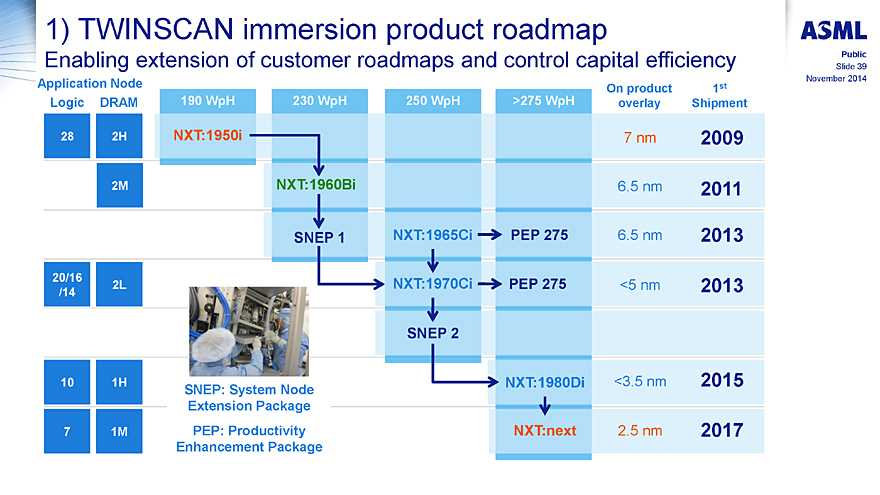

1) TWINSCAN immersion product roadmap

Enabling extension of customer roadmaps and control capital efficiency

Application Node On product 1st

Logic DRAM 190 WpH 230 WpH 250 WpH >275 WpH overlay Shipment

28 2H NXT:1950i 7 nm 2009

2M NXT:1960Bi 6.5 nm 2011

SNEP 1 NXT:1965Ci PEP 275 6.5 nm 2013

20/16/14 2L NXT:1970Ci PEP 275 <5 nm 2013

SNEP 2

10 1H NXT:1980Di <3.5 nm 2015

SNEP: System Node Extension Package

7 1M PEP: Productivity Enhancement Package NXT:next 2.5 nm 2017

�

ASML

Public

Slide 40

November 2014

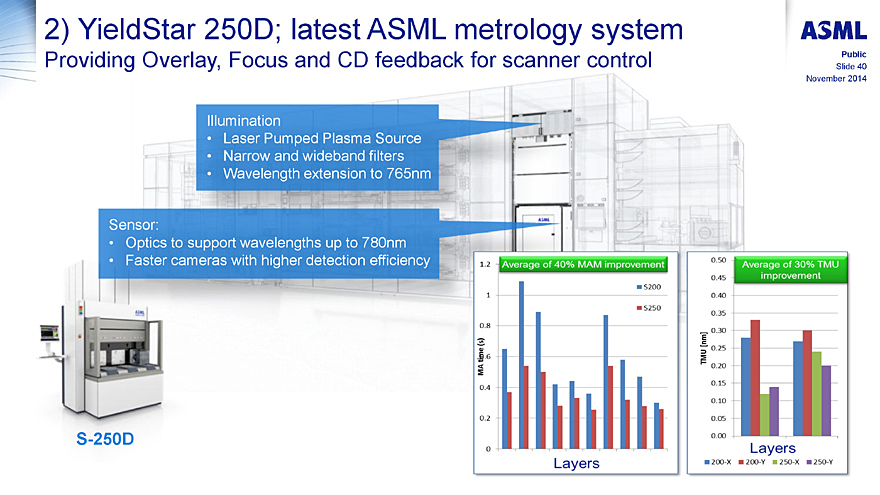

2) YieldStar 250D; latest ASML metrology system

Providing Overlay, Focus and CD feedback for scanner control

Illumination

� Laser Pumped Plasma Source

� Narrow and wideband filters

� Wavelength extension to 765nm

Sensor:

� Optics to support wavelengths up to 780nm

� Faster cameras with higher detection efficiency

S-250D

MA time(s)

Average of 40% MAM improvement

1.2

$200

1

$250

0.8

0.6

0.4

0.2

0

Layers

TMU [nm]

Average of 30% TMU improvement

0.50

0.45

0.40

0.35

0.30

0.25

0.20

0.15

0.10

0.05

0.00

Layers

200-X 200-Y 250-X 250-Y

�

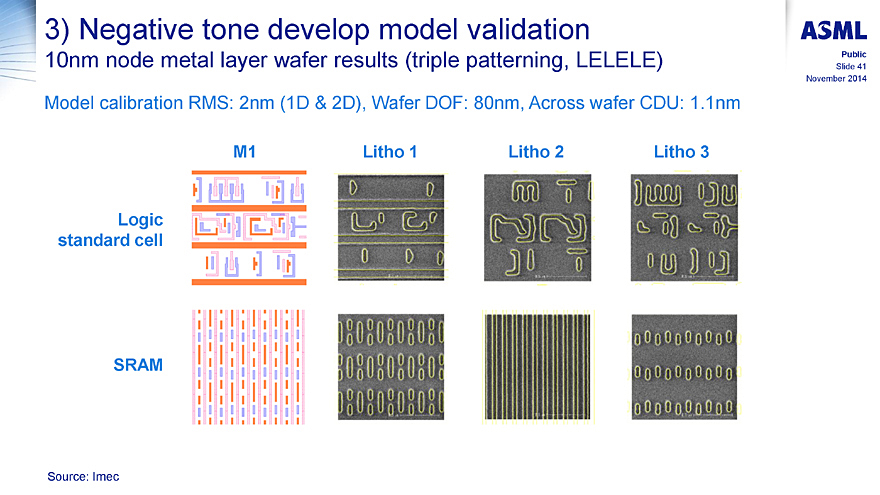

ASML

Public

Slide 41

November 2014

3) Negative tone develop model validation

10nm node metal layer wafer results (triple patterning, LELELE)

Model calibration RMS: 2nm (1D�& 2D), Wafer DOF: 80nm, Across wafer CDU: 1.1nm

M1

Litho 1

Litho 2

Litho 3

Logic standard cell

SRAM

Source: Imec

�

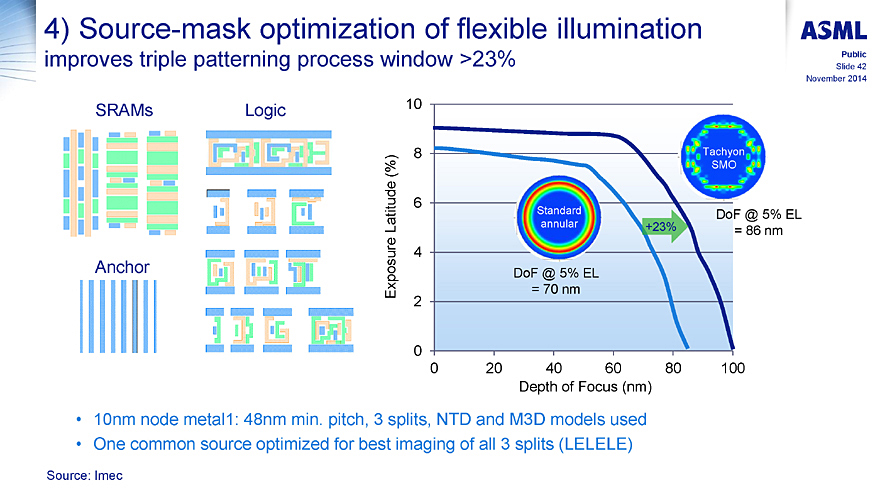

ASML

Public

Slide 42

November 2014

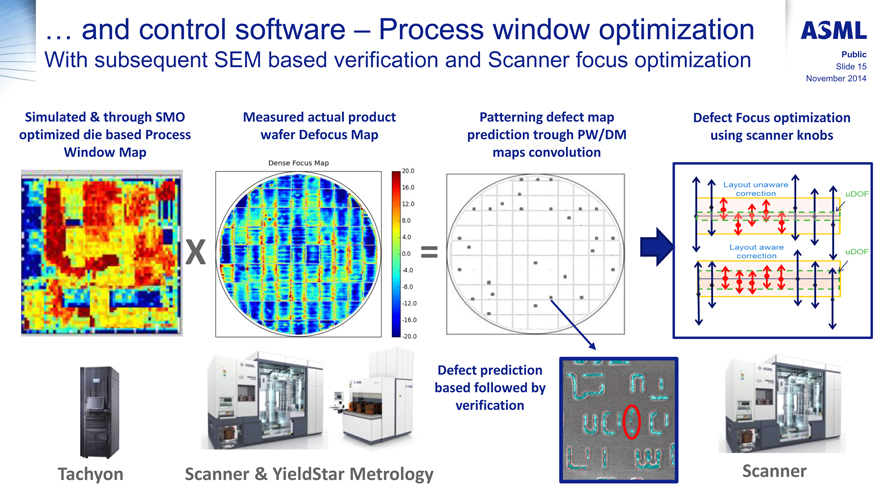

4) Source-mask optimization of flexible illumination improves triple patterning process window >23%

SRAMs

Logic

Anchor

Exposure Latitude (%)

10 8 6 4 2 0

Tachyon SMO

Standard annular

+23%

DoF @ 5% EL

= 86 nm

DoF @ 5% EL

= 70 nm

0

20

40

60

80

100

Depth of Focus (nm)

10nm node metal1: 48nm min. pitch, 3 splits, NTD and M3D models used

One common source optimized for best imaging of all 3 splits (LELELE)

Source: Imec

�

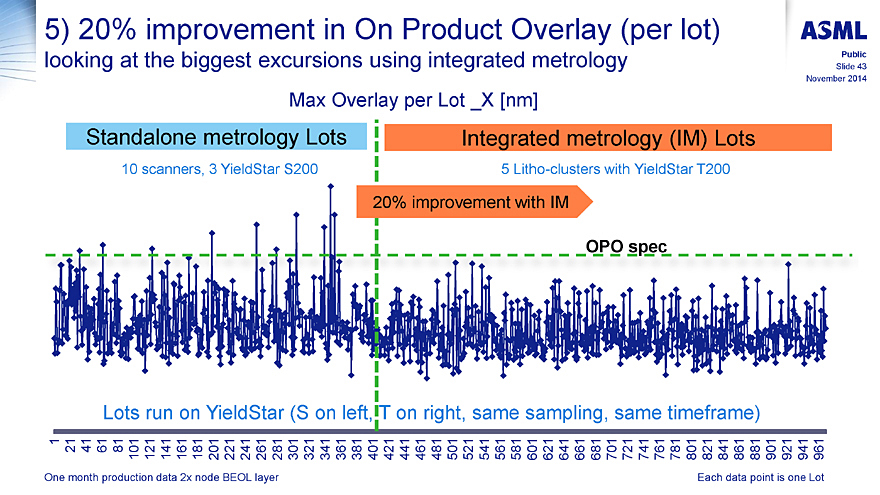

ASML

Public

Slide 43

November 2014

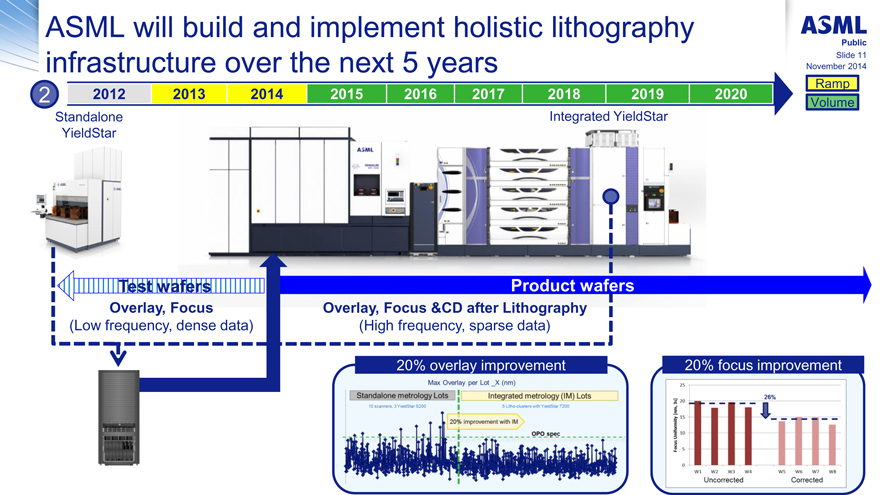

5) 20% improvement in On Product Overlay (per lot) looking at the biggest excursions using integrated metrology

Max Overlay per Lot _X [nm]

Standalone metrology Lots

10 scanners, 3 YieldStar S200

Integrated metrology (IM) Lots

5 Litho-clusters with YieldStar T200

20% improvement with IM

OPO spec

Lots run on YieldStar (S on left, T on right, same sampling, same timeframe)

1 21 41 61 81 101 121 141 161 181 201 221 241 261 281 301 321 341 361 381 401 421 441 461 481 501 521 541 561 581 601 621 641 661 681 701 721 741 761 781 801 821 841 861 881 901 921 941 961

One month production data 2x node BEOL layer

Each data point is one Lot

�

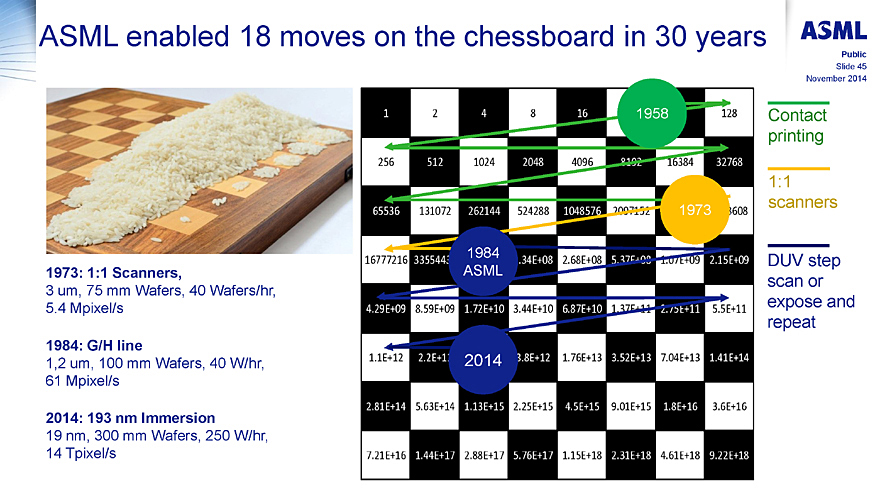

ASML

Public

Slide 44

November 2014

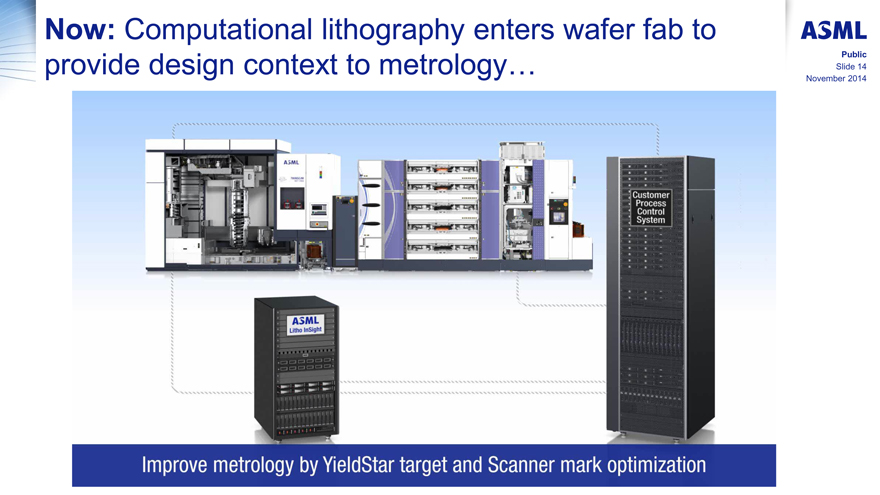

6) Computational lithography now enters the fab provide metrology context reducing target and recipe design qualification

Overlay simulated and measured on customer product wafers of various markers and recipe combinations

� Physical overlay (measured) vs. Overlay accuracy KPI (simulated)

Physical overlay (measured) vs. TMU

Overlay accuracy KPI, simulated, [nm]

16 14 12 10 8 6 4 2 0

R2 = 0.8719

R2 = 0.3914

0.7 0.7 0.6 0.6 0.5 0.5 0.4 0.4 0.3 0.3

0 2 4 6 8 10 12 14 16

Total Measurement Uncertainty, TMU, [nm] (Reproducibility + 0-180� offset) measured,

Physical overlay, measured [nm]

Physical overlay measurement (SEM)

Overlay accuracy KPI Simulated

DSWA

Floor Tilt

Overlay (Accuracy) KPI:

OVL

Asymi

Asymi = {DSWA, Floor tilt,�}

MIN Marker, recipe

Overlay KPI (marker, recipe)

�

ASML

Public

Slide 45

November 2014

ASML enabled 18 moves on the chessboard in 30 years

1973: 1:1 Scanners,

3 um, 75 mm Wafers, 40 Wafers/hr,

5.4 Mpixel/s

1984: G/H line

1,2 um, 100 mm Wafers, 40 W/hr,

61 Mpixel/s

2014: 193 nm Immersion

19 nm, 300 mm Wafers, 250 W/hr,

14 Tpixel/s

1 2 4 8 16 1958 128

256 512 1024 2048 4096 8192 16384 32768

65536 131072 262144 524288 1048576 2097152 1973 8608

16777216 3355443 1984 ASML .34E+08 2.68E+08 5.37E+08 1.07E+09 2.15E+09

4.29E+09 8.59E+09 1.72E+10 3.44E+10 6.87E+10 1.37E+11 2.75E+11 5.5E+11

1.1E+12 2.2E+12 2014 .8E+12 1.76E+13 3.52E+13 7.04E+13 1.41E+14

2.81E+14 5.63E+14 1.13E+15 2.25E+15 4.5E+15 9.01E+15 1.8E+16 3.6E+16 7.21E+16

1.44E+17 2.88E+17 5.76E+17 1.15E+18 2.31E+18 4.61E+18 9.22E+18

Contact printing

1:1 scanners

DUV step scan or expose and repeat

�

ASML

Public

Slide 46

November 2014

Multi-patterning could explode, but EUV will simplify through less patterning and metrology steps

Layers

5A 4A 3A 21A 1A 0A

Masks

Layers

5A 4A 3A 3B 21A 1A 0A 0B

Masks

Layers

5A 5B 5C

4A 4B 4C

3A 3B 3C 3D

21A 21B 22A 22B

1A 1B 1C 1D

0A 0B 0C 0D 0E

5A 4A 3A 21A 22A 1A 1B 0A 0B

Masks

Layers

EUV

Masks

Node

28nm

20nm

10nm

7nm all immersion

7nm all EUV

# of lithography steps 6 8 23 34 9

# OVL metrology 7 9-11 36-40 59-65 12

�

ASML

Public

Slide 47

November 2014

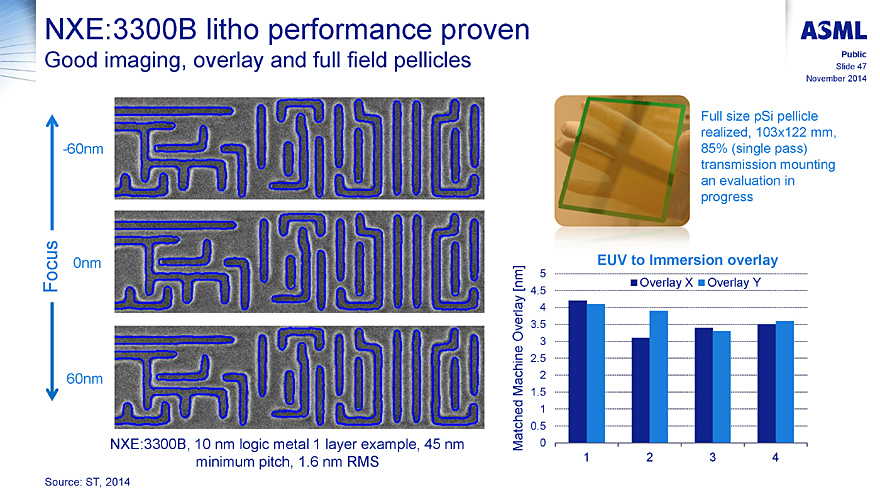

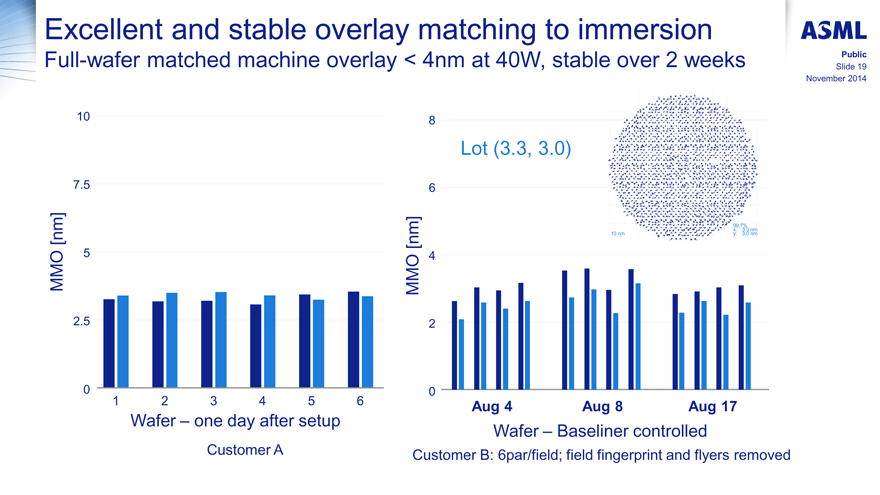

NXE:3300B litho performance proven

Good imaging, overlay and full field pellicles

Focus

-60nm

0nm

60nm

NXE:3300B, 10 nm logic metal 1 layer example, 45 nm minimum pitch, 1.6 nm RMS

Full size pSi pellicle

realized, 103x122 mm,

85% (single pass)

transmission mounting

an evaluation in

progress

Matched Machine Overlay [nm]

5 4.5 4 3.5 3 2.5 2 1.5 1 0.5 0

EUV to Immersion overlay

Overlay X

Overlay Y

1 2 3 4

Source: ST, 2014

�

ASML

Public

Slide 48

November 2014

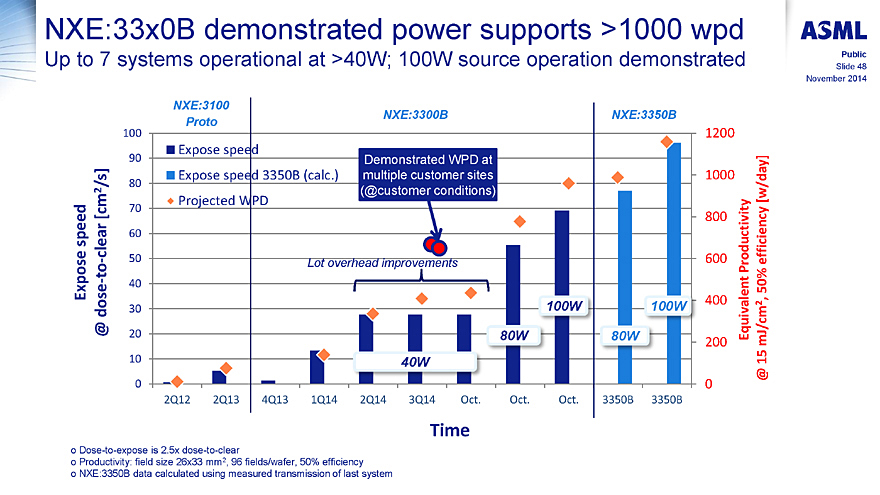

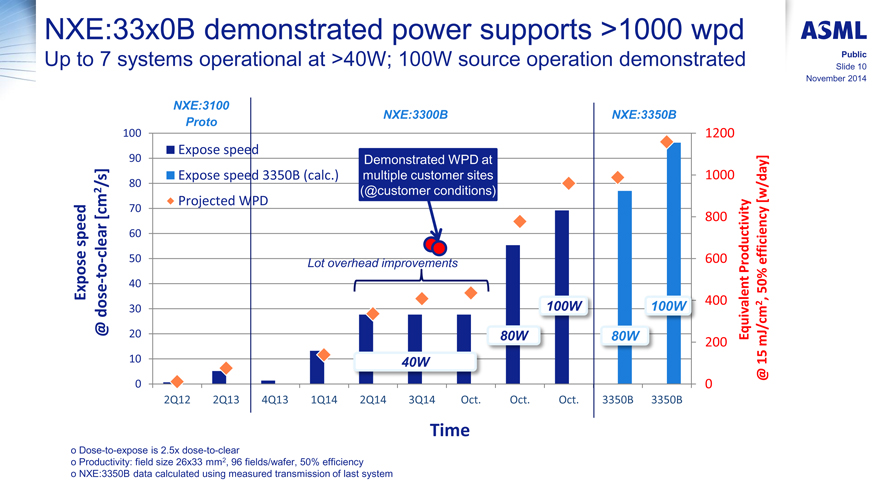

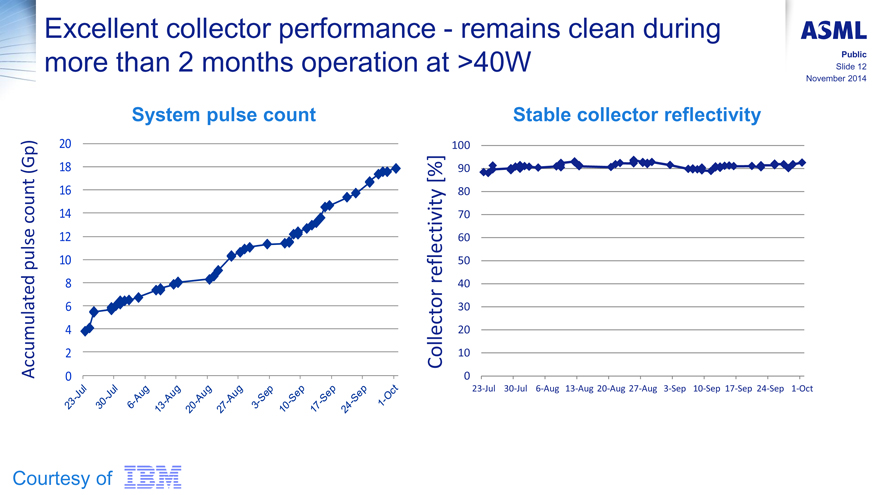

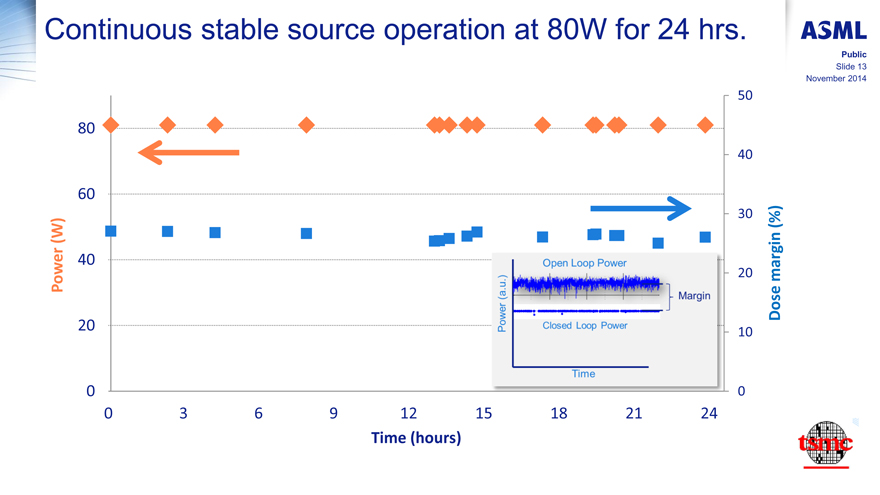

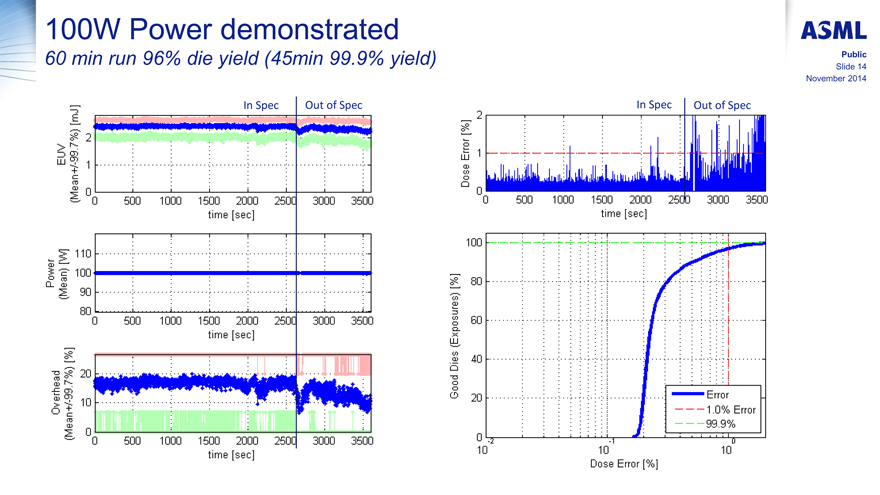

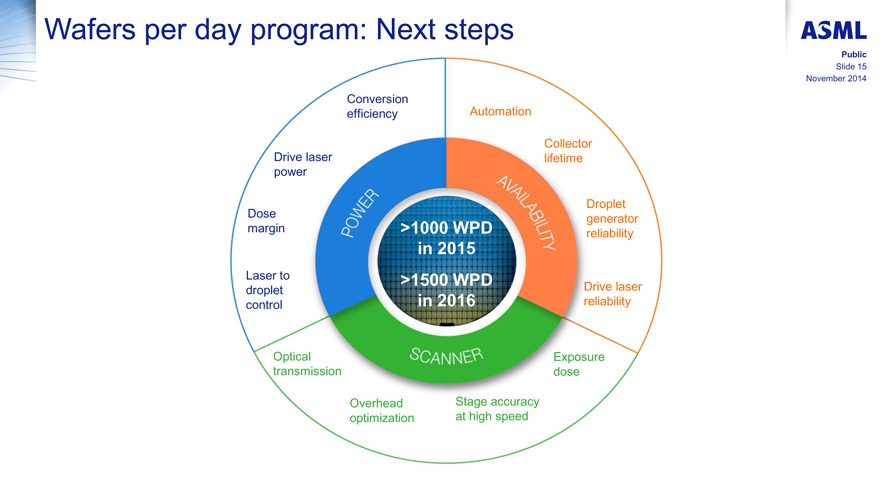

NXE:33x0B demonstrated power supports >1000 wpd

Up to 7 systems operational at >40W; 100W source operation demonstrated

Exposed speed @ dose-to-clear (cm2/s]

100 90 80 70 60 50 40 30 20 10 0

NXE:3100

Proto

Expose speed

Expose speed 3350B (calc.)

Projected WPD

NXE:3300B

Demonstrated WPD at multiple customer sites

(@customer conditions)

Lot overhead improvements

NXE:3350B

40W 80W 100W 80W 100W

1200 1000 800 600 400 200 0

Equivalent Productivity @ 15 mJ/cm2, 50% efficiency [w/day]

2Q12 2Q13 4Q13 1Q14 2Q14 3Q14 Oct. Oct. Oct. 3350B 3350B

Time

o Dose-to-expose is 2.5x dose-to-clear

o Productivity: field size 26x33 mm2, 96 fields/wafer, 50% efficiency

o NXE:3350B data calculated using measured transmission of last system

�

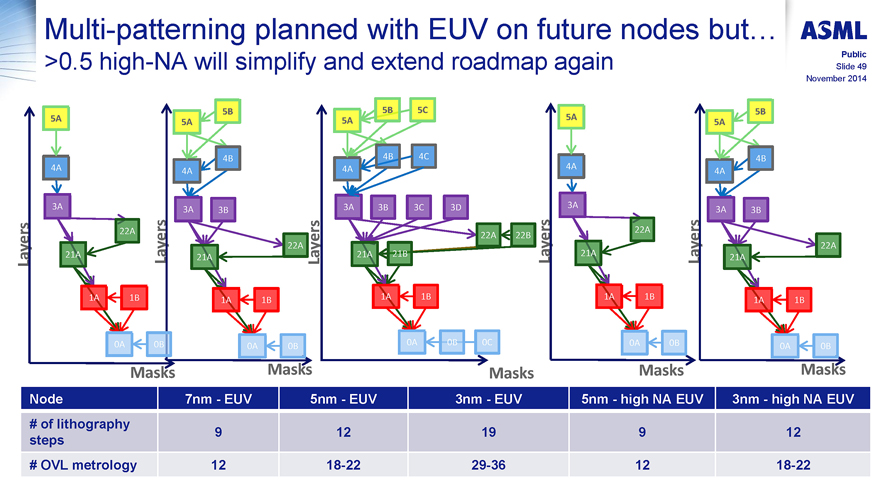

Multi-patterning planned with EUV on future nodes but�

>0.5 high-NA will simplify and extend roadmap again

ASML

Public

Slide 49

November 2014

Layers

5A 4A 3A 22A 21A 1A 1B 0A 0B

Masks

Layers

5B 5A 4B 4A 3A 3B 22A 21A 1A 1B 0A 0B

Masks

Layers

5B 5C 5A 4B 4C 4A 3A 3B 3C 3D 22A 22B 21A 21B 1A 1B 0A 0B 0C

Masks

Layers

5A 4A 3A 22A 21A 1A 1B 0A 0B

Masks

Layers

5B 5A 4B 4A 3A 3B 22A 21A 1A 1B 0A 0B

Masks

Node

7nm - EUV

5nm - EUV

3nm - EUV

5nm - high NA EUV

3nm - high NA EUV

# of lithography steps

9 12 19 9 12

# OVL metrology

12 18-22 29-36 12 18-22

�

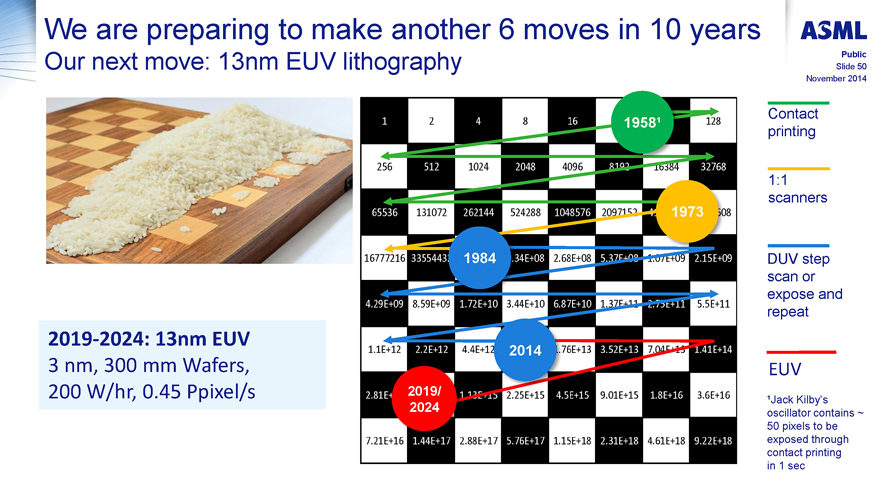

We are preparing to make another 6 moves in 10 years

Our next move: 13nm EUV lithography

ASML

Public

Slide 50

November 2014

2019-2024: 13nm EUV

3 nm, 300 mm Wafers,

200 W/hr, 0.45 Ppixel/s

1 2 4 8 16 128

256 512 1024 2048 4096 8192 16384 32768

65536 131072 262144 524288 1048576 2097152 4 608

16777216 3355443 .34E+08 2.68E+08 5.37E+08 1.07E+09 2.15E+09

4.29E+09 8.59E+09 1.72E+10 3.44E+10 6.87E+10 1.37E+11 2.75E+11 5.5E+11

1.1E+12 2.2E+12 4.4E+12 .76E+13 3.52E+13 7.04E+13 1.41E+14

2.81E+ 1.13E+15 2.25E+15 4.5E+15 9.01E+15 1.8E+16 3.6E+16

7.21E+16 1.44E+17 2.88E+17 5.76E+17 1.15E+18 2.31E+18 4.61E+18 9.22E+18

19581

1973

1984

2014

2019/2024

Contact printing

1:1 scanners

DUV step scan or expose and repeat

EUV

1Jack Kilby�s oscillator contains ~ 50 pixels to be exposed through contact printing in 1 sec

�

Summary

ASML

Public

Slide 51

November 2014

Node progression enabled by immersion multi pass patterning and extended litho metrology and computational litho to control complexity

To address highly complex multi-patterning schemes, EUV insertion is likely at the 10nm logic and 7nm MPU node with full production one node later

ASML has demonstrated consistent EUV source progress. Today performance approaching 100W exposure power. System uptime remains a key challenge

EUV infrastructure supportive for above transition scenarios

Lithography roadmap defined down to the 3nm node

�

Had the King�s name been Moore�.

ASML

Public

Slide 52

November 2014

He would have worked to find ways to scale down his grains, keep their nutritional value and double the amount with every move.

He could have fed the world, instead of having lost a Kingdom.

�

ASML

INVESTOR DAY

ASMLSMALLTALK2014

LONDON

Exhibit 99.4

�

�

ASML

DUV

Matthew McLaren

Vice President Program Management, DUV

24 November 2014

INVESTOR DAY

ASML SMALLTALK2014

LONDON

�

ASML

Public

Slide 2 November 2014

Forward looking statements

This document contains statements relating to certain projections and business trends that are forward-looking, including statements with respect to our outlook, expected customer demand in specified market segments, expected sales levels and trends, our market share, customer orders and systems backlog, IC unit demand, expected or indicative financial results or targets, including revenue, gross margin, expenses, gross margin percentage, opex percentage of sales, tax percentage, cash conversion cycle, capex percentage of sales, credit rating and earnings per share, expected shipments of tools and the timing thereof, including expected shipments of EUV and DUV tools, productivity of our tools and systems performance, including EUV system performance (such as endurance tests), the development of EUV technology and timing of shipments, development in IC technology, including shrink scenarios, NAND technology development and cost estimates, expectations on development of the shrink roadmap across all of our systems, upgradeability of our tools, system orders, customer transition estimates, expected transition scaling, forecasted industry developments, including expected smartphone, tablet and server use in future years, and expectations relating to new applications including wearable devices and connected devices, expected investment pay-back time for foundries, expected construction of additional holistic lithography infrastructure, the continuation of Moore�s Law, and our dividend policy and intention to repurchase shares. You can generally identify these statements by the use of words like �may�, �will�, �could�, �should�, �project�, �believe�, �anticipate�, �expect�, �plan�, �estimate�, �forecast�, �potential�, �intend�, �continue� and variations of these words or comparable words. These statements are not historical facts, but rather are based on current expectations, estimates, assumptions and projections about the business and our future financial results and readers should not place undue reliance on them.

Forward-looking statements do not guarantee future performance and involve risks and uncertainties. These risks and uncertainties include, without limitation, economic conditions, product demand and semiconductor equipment industry capacity, worldwide demand and manufacturing capacity utilization for semiconductors (the principal product of our customer base), the impact of general economic conditions on consumer confidence and demand for our customers� products, competitive products and pricing, affordability of shrink, the continuation of Moore�s Law, the impact of manufacturing efficiencies and capacity constraints, performance of our systems, the continuing success of technology advances and the related pace of new product development and customer acceptance of new products and customers meeting their own development roadmaps, market demand for our existing products and for new products and our ability to maintain or increase or market share, the development of and customer demand for multi-patterning technology and our ability to meet overlay and patterning requirements, the number and timing of EUV systems expected to be shipped, our ability to enforce patents and protect intellectual property rights, the risk of intellectual property litigation, EUV system performance and customer acceptance, availability of raw materials and critical manufacturing equipment, trade environment, our ability to reduce costs, changes in exchange rates and tax rates, available cash, distributable reserves for dividend payments and share repurchases, changes in our treasury policy, including our dividend and repurchase policy, completion of sales orders, the risk that key assumptions underlying financial targets prove inaccurate, including assumptions relating to market share, lithography market growth and our customers� ability to reduce productions costs, risks associated with Cymer, which we acquired in 2013, and other risks indicated in the risk factors included in ASML�s Annual Report on Form 20-F and other filings with the US Securities and Exchange Commission. These forward-looking statements are made only as of the date of this document. We do not undertake to update or revise the forward-looking statements, whether as a result of new information, future events or otherwise.

�

ASML

Public

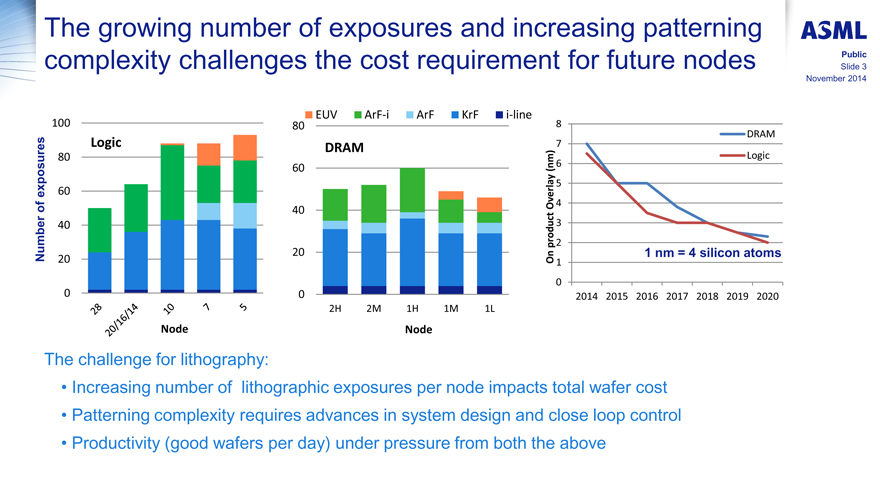

Slide 3 November 2014

The growing number of exposures and increasing patterning complexity challenges the cost requirement for future nodes

Number of exposures

Logic 100 80 60 40 20 0 28 20/16/2014 10 7 5 Node

EUV ArF-i ArF KrF i-line

DRAM 80 60 40 20 0 2H 2M 1H 1M 1L Node

On product Overlay (nm)

DRAM Logic

8 7 6 5 4 3 2 1 0

1 nm = 4 silicon atoms

2014 2015 2016 2017 2018 2019 2020

The challenge for lithography:

Increasing number of lithographic exposures per node impacts total wafer cost

Patterning complexity requires advances in system design and close loop control

Productivity (good wafers per day) under pressure from both the above

�

ASML

Public

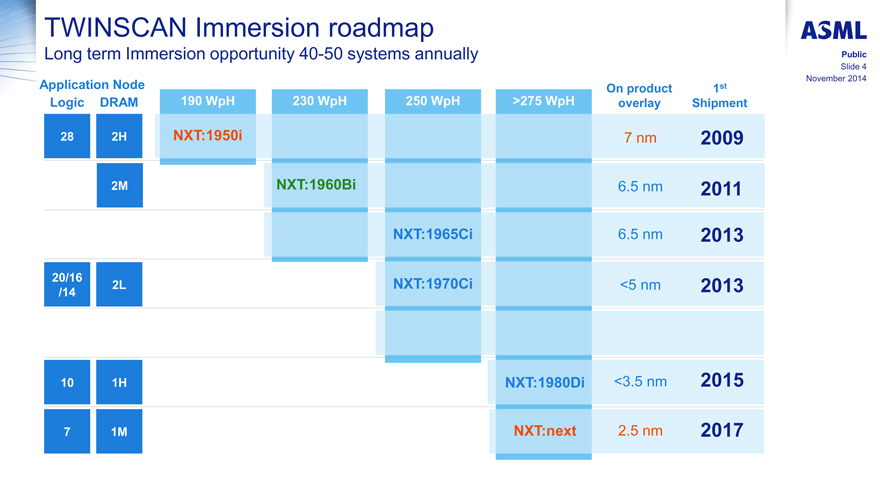

Slide 4 November 2014

TWINSCAN Immersion roadmap

Long term Immersion opportunity 40-50 systems annually

Application Node Logic DRAM

190 WpH 230 WpH 250 WpH >275 WpH

On product overlay 1st Shipment

28 2H NXT:1950i 7 nm 2009

2M NXT:1960Bi 6.5 nm 2011

NXT:1965Ci 6.5 nm 2013

20/16/14 2L NXT:1970Ci <5 nm 2013

10 1H NXT:1980Di <3.5 nm

2015 7 1M NXT:next 2.5 nm 2017

�

ASML

Public

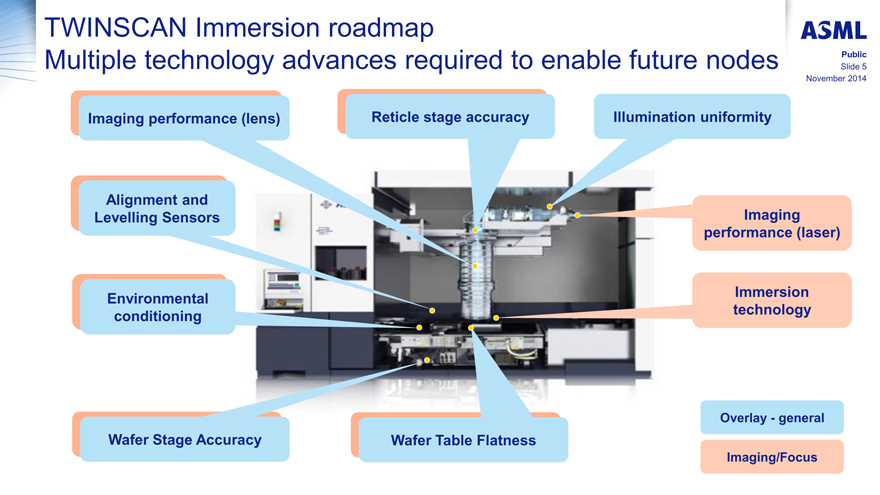

Slide 5 November 2014

TWINSCAN Immersion roadmap

Multiple technology advances required to enable future nodes

Imaging performance (lens)

Reticle stage accuracy

Illumination uniformity

Alignment and Levelling Sensors

Imaging performance (laser)

Environmental conditioning

Immersion technology

Overlay - general

Wafer Stage Accuracy

Wafer Table Flatness

Imaging/Focus

�

ASML

Public

Slide 6 November 2014

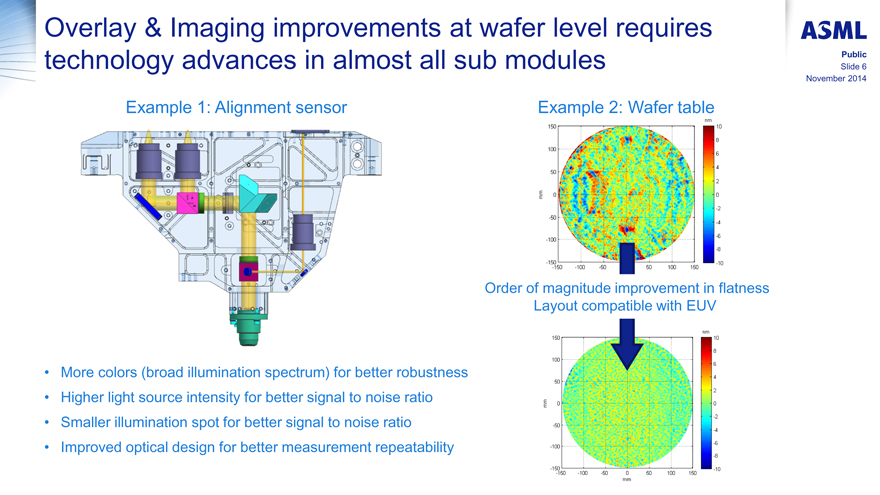

Overlay & Imaging improvements at wafer level requires technology advances in almost all sub modules

Example 1: Alignment sensor

More colors (broad illumination spectrum) for better robustness

Higher light source intensity for better signal to noise ratio

Smaller illumination spot for better signal to noise ratio

Improved optical design for better measurement repeatability

Example 2: Wafer table

mm 150 100 50 0 -50 -100 -150

nm 10 8 6 4 2 0 -2 -4 -6 -8

-150 -100 -50 50 100 150 -10

Order of magnitude improvement in flatness Layout compatible with EUV

mm 150 100 50 0 -50 -100 -150

nm 10 8 6 4 2 0 -2 -4 -6 -8 -10

-150 -100 -50 0 50 100 150 mm

�

ASML

Public

Slide 7 November 2014

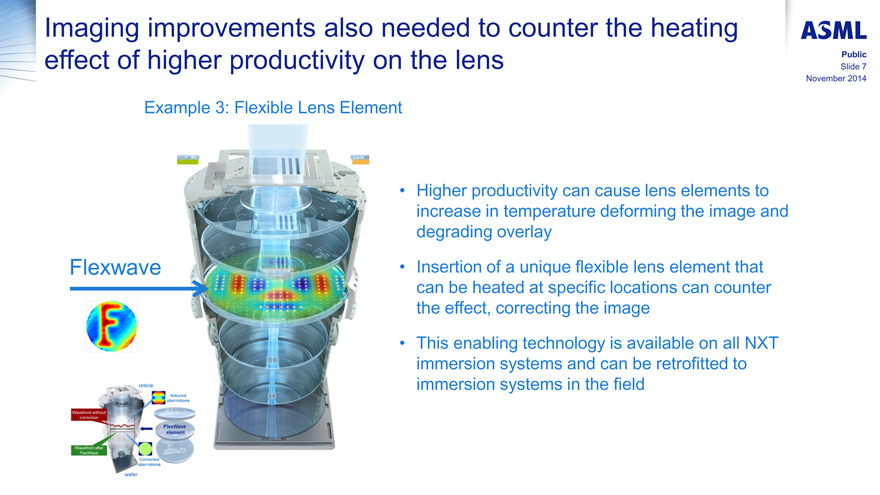

Imaging improvements also needed to counter the heating effect of higher productivity on the lens

Example 3: Flexible Lens Element

Flexwave

Higher productivity can cause lens elements to increase in temperature deforming the image and degrading overlay

Insertion of a unique flexible lens element that can be heated at specific locations can counter the effect, correcting the image

This enabling technology is available on all NXT immersion systems and can be retrofitted to immersion systems in the field

�

ASML

Public

Slide 8 November 2014

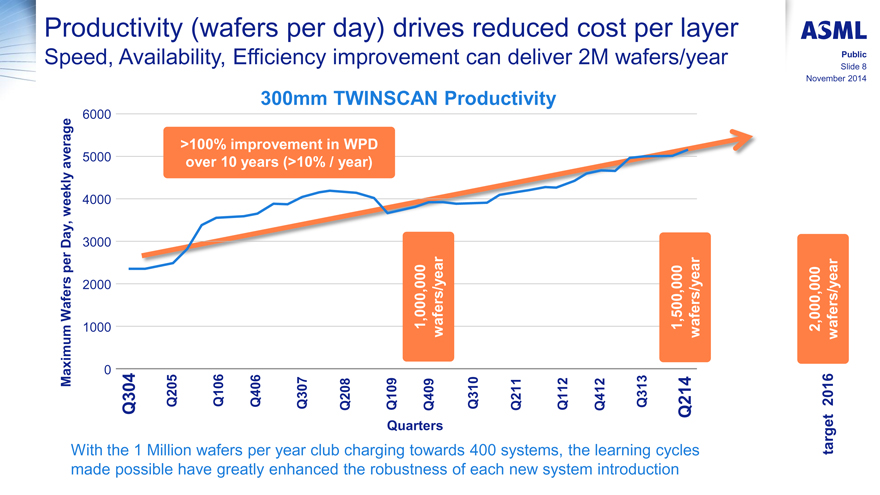

Productivity (wafers per day) drives reduced cost per layer

Speed, Availability, Efficiency improvement can deliver 2M wafers/year

300mm TWINSCAN Productivity

Maximum Wafers per Day, weekly average

6000 5000 4000 3000 2000 1000 0

>100% improvement in WPD over 10 years (>10% / year)

1,000,000 wafers/year

1,500,000 wafers/year

2,000,000 wafers/year

Q304 Q205 Q106 Q406 Q307 Q208 Q109 Q409 Q310 Q211 Q112 Q412 Q313 Q214 Target 2016

With the 1 Million wafers per year club charging towards 400 systems, the learning cycles made possible have greatly enhanced the robustness of each new system introduction

�

ASML

Public

Slide 9

November 2014

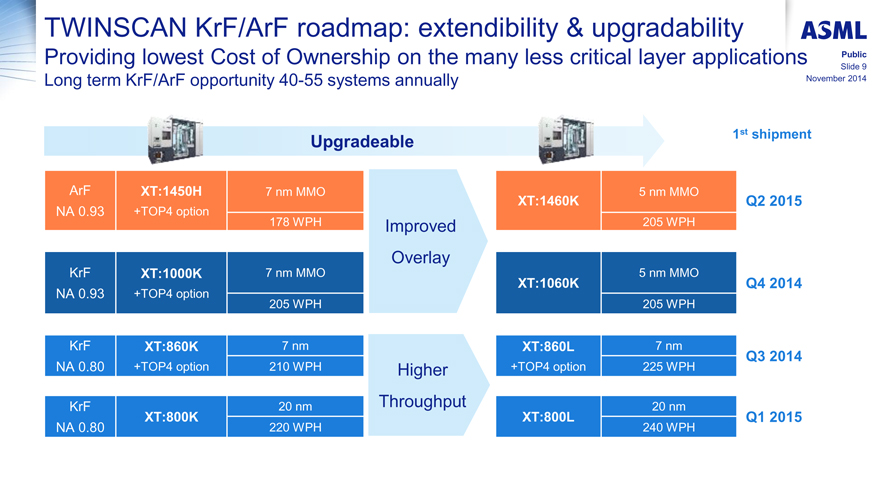

TWINSCAN KrF/ArF roadmap: extendibility�& upgradability

Providing lowest Cost of Ownership on the many less critical layer applications

Long term KrF/ArF opportunity 40-55 systems annually

Upgradeable 1st shipment

ArF XT:1450H 7 nm MMO 5 nm MMO

XT:1460K Q2 2015

NA 0.93 +TOP4 option

178 WPH Improved Overlay 205 WPH

KrF XT:1000K 7 nm MMO 5 nm MMO

XT:1060K Q4 2014

NA 0.93 +TOP4 option

205 WPH 205 WPH

KrF XT:860K 7 nm XT:860L 7 nm

Q3 2014

NA 0.80 +TOP4 option 210 WPH Higher +TOP4 option 225 WPH

KrF 20 nm Throughput 20 nm

XT:800K XT:800L Q1 2015

NA 0.80 220 WPH 240 WPH

�

ASML

Public

Slide 10

November 2014

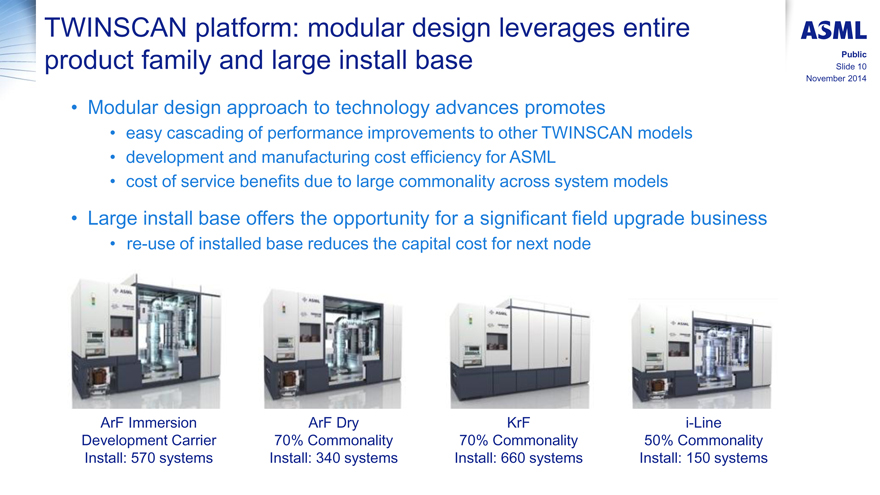

TWINSCAN platform: modular design leverages entire product family and large install base

Modular design approach to technology advances promotes

easy cascading of performance improvements to other TWINSCAN models

development and manufacturing cost efficiency for ASML

cost of service benefits due to large commonality across system models

Large install base offers the opportunity for a significant field upgrade business

re-use of installed base reduces the capital cost for next node

ArF Immersion ArF Dry KrF i-Line

Development Carrier 70% Commonality 70% Commonality 50% Commonality

Install: 570 systems Install: 340 systems Install: 660 systems Install: 150 systems

�

ASML

Public

Slide 11

November 2014

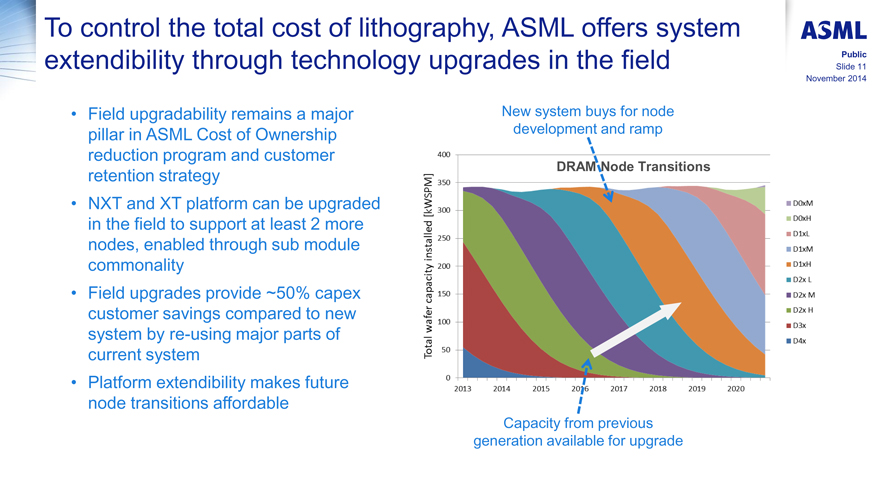

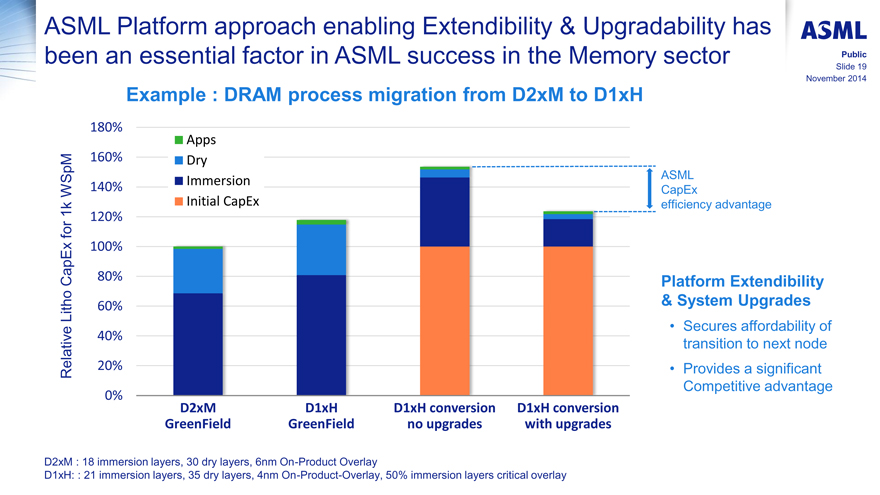

To control the total cost of lithography, ASML offers system extendibility through technology upgrades in the field

Field upgradability remains a major pillar in ASML Cost of Ownership reduction program and customer retention strategy

NXT and XT platform can be upgraded in the field to support at least 2 more nodes, enabled through sub module commonality

Field upgrades provide ~50% capex customer savings compared to new system by re-using major parts of current system

Platform extendibility makes future node transitions affordable

New system buys for node development and ramp

Total wafer capacity installed [kWSPM] 400

350 DRAM Node Transitions D0xM

D0xH

D1xL

300 D1xM

250 D1xH

200 D2x L

150 D2x M

100 D2x H

50 D3x

0 D4x

2013 2014 2015 2016 2017 2018 2019 2020

Capacity from previous generation available for upgrade

�

ASML

Public

Slide 12

November 2014

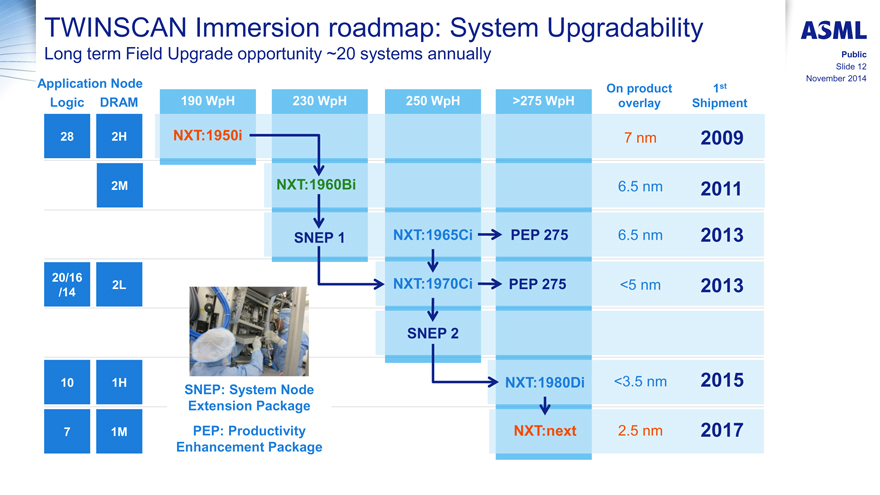

TWINSCAN Immersion roadmap: System Upgradability

Long term Field Upgrade opportunity ~20 systems annually

Application Node On product 1st

Logic DRAM 190 WpH 230 WpH 250 WpH >275 WpH overlay Shipment

28 2H NXT:1950i 7 nm 2009

2M NXT:1960Bi 6.5 nm 2011

SNEP 1 NXT:1965Ci PEP 275 6.5 nm 2013

20/16 2L NXT:1970Ci PEP 275 <5 nm 2013

/14

SNEP 2

10 1H NXT:1980Di <3.5 nm 2015

SNEP: System Node

Extension Package

7 1M PEP: Productivity NXT:next 2.5 nm 2017

Enhancement Package

�

ASML

Public

Slide 13

November 2014

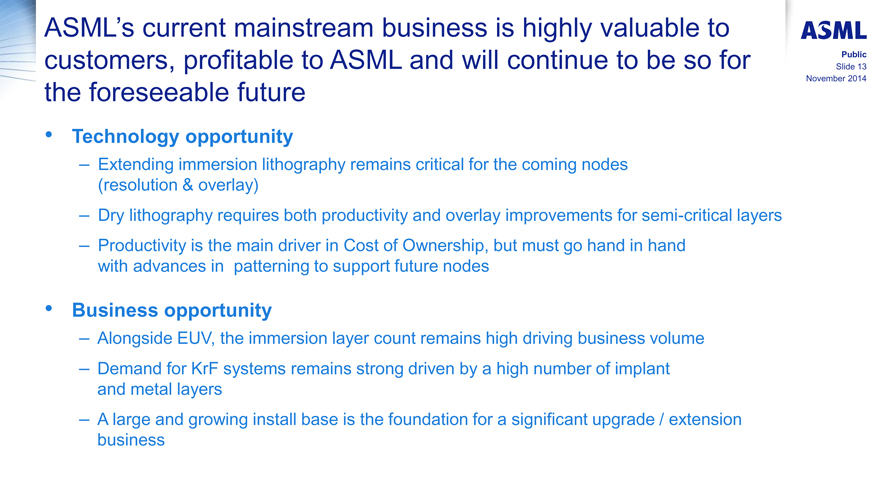

ASML�s current mainstream business is highly valuable to customers, profitable to ASML and will continue to be so for the foreseeable future

Technology opportunity

Extending immersion lithography remains critical for the coming nodes (resolution�& overlay)

Dry lithography requires both productivity and overlay improvements for semi-critical layers

Productivity is the main driver in Cost of Ownership, but must go hand in hand with advances in patterning to support future nodes

Business opportunity

Alongside EUV, the immersion layer count remains high driving business volume

Demand for KrF systems remains strong driven by a high number of implant and metal layers

A large and growing install base is the foundation for a significant upgrade / extension business

�

ASML

INVESTOR DAY

ASMLSMALLTALK2014

LONDON

Exhibit 99.5

�

�

ASML

Holistic Lithography

Christophe Fouquet

Executive Vice President, Applications

24�November 2014

INVESTOR DAY

ASMLSMALLTALK2014

LONDON

�

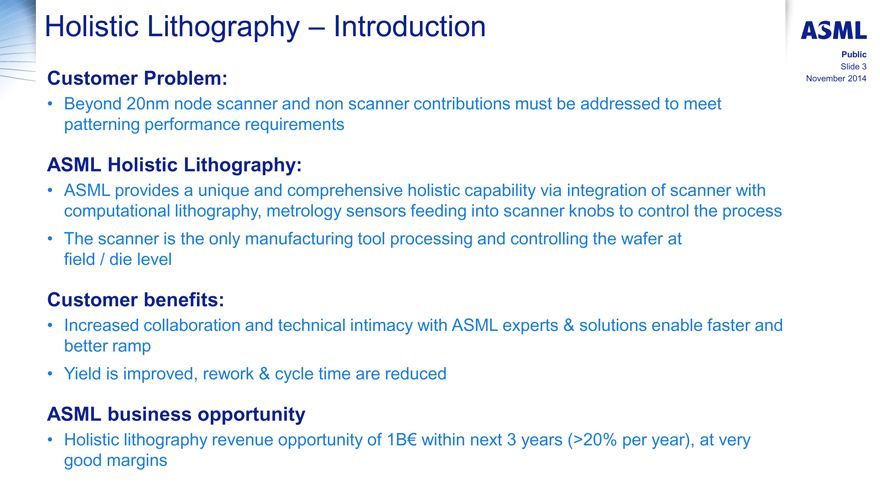

ASML

Public

Slide 3

November 2014

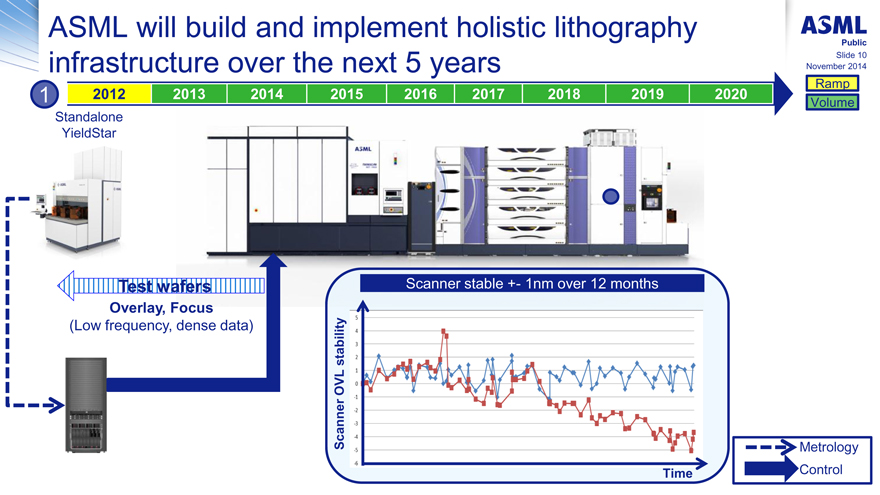

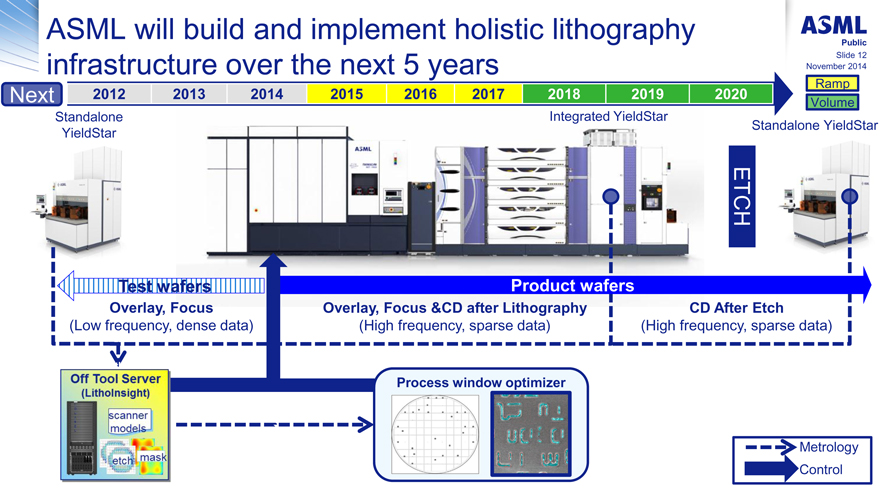

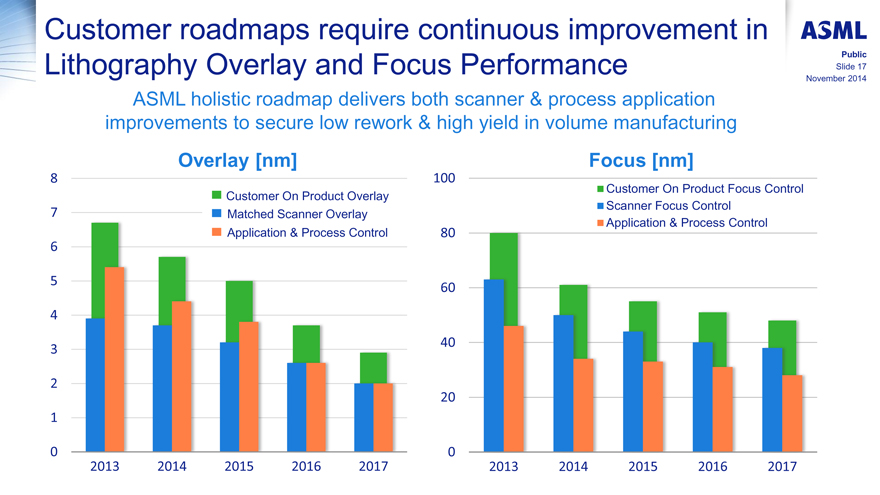

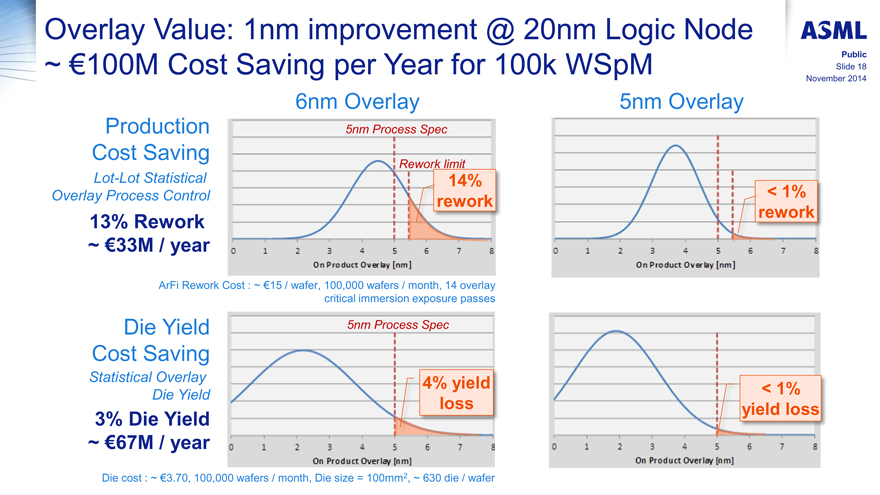

Holistic Lithography � Introduction

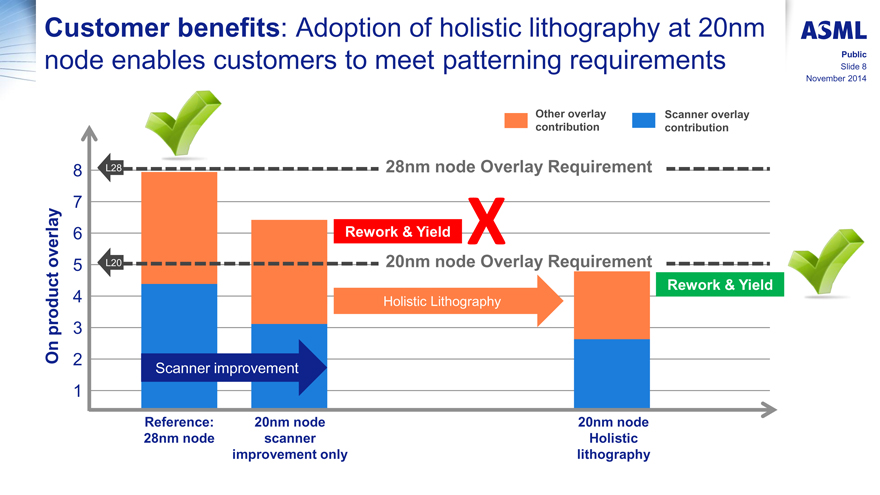

Customer Problem:

Beyond 20nm node scanner and non scanner contributions must be addressed to meet patterning performance requirements

ASML Holistic Lithography:

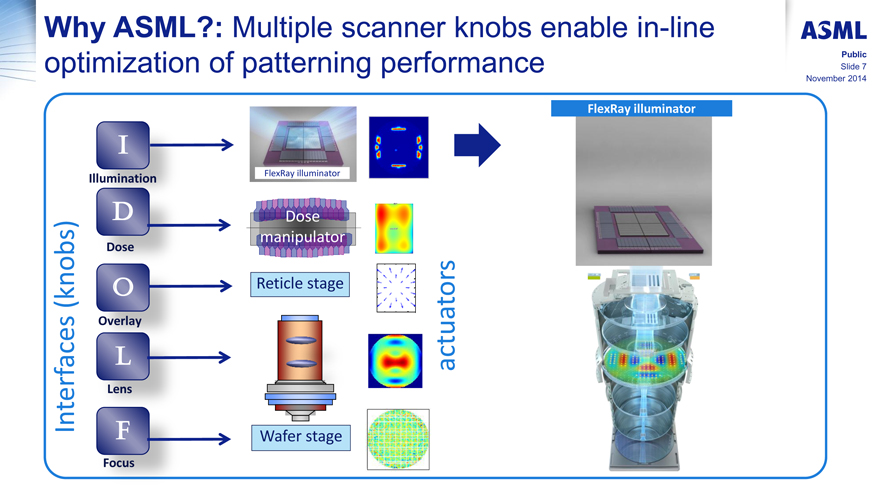

ASML provides a unique and comprehensive holistic capability via integration of scanner with computational lithography, metrology sensors feeding into scanner knobs to control the process

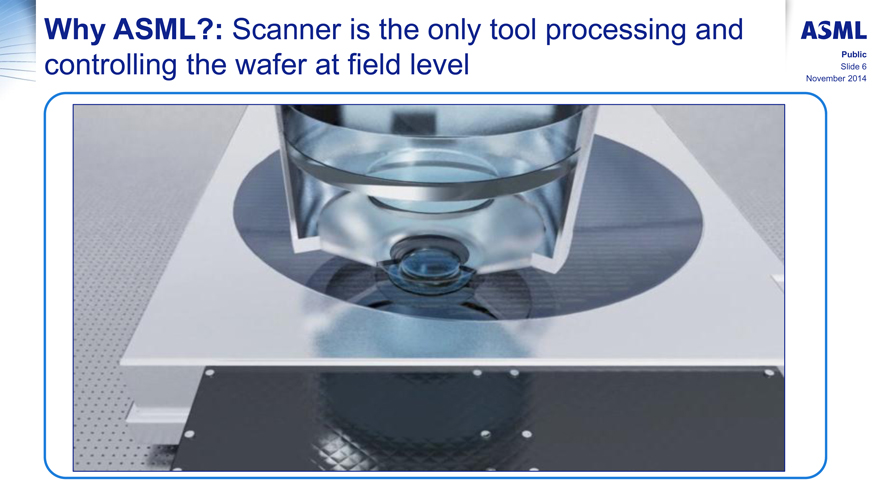

The scanner is the only manufacturing tool processing and controlling the wafer at field / die level

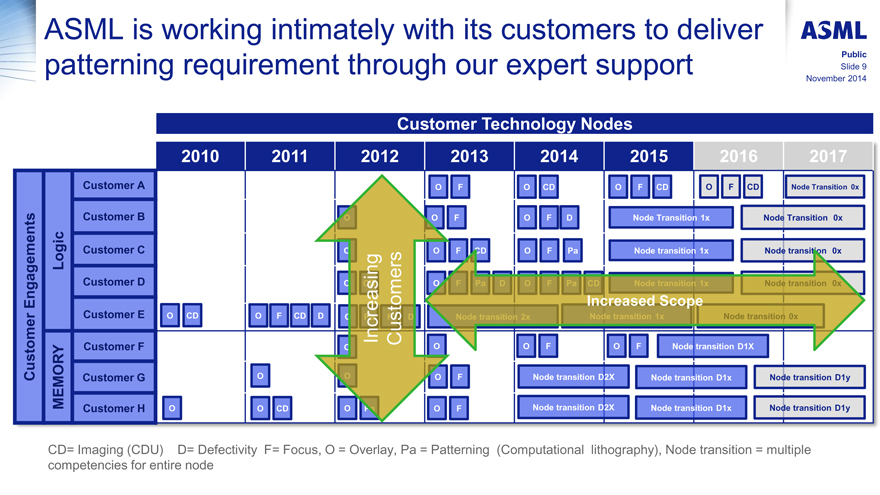

Customer benefits:

Increased collaboration and technical intimacy with ASML experts�& solutions enable faster and better ramp